# E-GOLDradio

GSM/GPRS Single Chip Solution

PMB 7870

V1.00

J. S. J. S.

Secure Mobile Solutions

#### Edition 2005-12-07

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany

© Infineon Technologies AG 2005.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

# Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# E-GOLDradio GSM/GPRS Single Chip Solution PMB 7870 V1.00

Secure Mobile Solutions

# **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

smsdocu.comments@infineon.com

# **CONFIDENTIAL**

| 1                      | Introduction                           |     |

|------------------------|----------------------------------------|-----|

| 1.1                    | Overview                               | . 9 |

| 1.2                    | Algorithm Partitioning                 | 10  |

| 1.3                    | Scheduler Functions                    | 10  |

| 2                      | Booting                                | 13  |

| <del>-</del><br>2.1    | Boot Concept                           |     |

| 2.2                    | Normal Boot Procedure                  |     |

| 2.3                    | Fast Boot Procedure                    |     |

| 2.4                    | Firmware ID and DSP Subsystem ID       |     |

| 2. <del>4</del><br>2.5 | Startup-Code Version                   |     |

|                        | ·                                      |     |

| 3                      | Commands                               | _   |

| 3.1                    | DSP Subsystem Command Interface to MCU |     |

| 3.2                    | List of Commands                       |     |

| 3.3                    | Command Description                    |     |

| 3.3.1                  | FC_INIT                                |     |

| 3.3.2                  | MODU_INIT                              |     |

| 3.3.3                  | IQ_SWAP_1                              |     |

| 3.3.4                  | IQ_SWAP_2                              |     |

| 3.3.5                  | DEC_INIT                               | 36  |

| 3.3.6                  | CIPH_KEY                               | 41  |

| 3.3.7                  | CCH_RX                                 | 42  |

| 3.3.8                  | CCH_TX                                 | 42  |

| 3.3.9                  | TCH_26                                 | 43  |

| 3.3.10                 | LOOP                                   | 46  |

| 3.3.11                 | PDCH                                   | 46  |

| 3.3.12                 | BB OFF                                 |     |

| 3.3.13                 | IDLE                                   | 48  |

| 3.3.14                 | VB ON                                  |     |

| 3.3.15                 | VB SET BIQUAD                          |     |

| 3.3.16                 | VB SET GAIN                            |     |

| 3.3.17                 | VB START TONE                          |     |

| 3.3.18                 | VB STOP TONE                           |     |

| 3.3.19                 | VB READ DURATION                       |     |

| 3.3.20                 | VB RESET                               |     |

| 3.3.21                 | VB_DAI                                 |     |

| 3.3.22                 | HF SET PAR                             |     |

| 3.3.23                 | HF_ON                                  |     |

| 3.3.24                 | VM CMD                                 |     |

| 3.3.25                 | VB SET CBUF GAIN                       |     |

| 3.3.26                 | DTX_ON                                 |     |

| 3.3.27                 | PW DOWN                                |     |

| 3.3.28                 | WRITE DSP                              |     |

| 3.3.29                 | READ DSP                               |     |

| 3.3.30                 | WRITE PROG                             |     |

| 3.3.31                 | READ PROG                              |     |

| 3.3.32                 | MCU INT                                |     |

| 3.3.32<br>3.3.33       | <del>-</del>                           |     |

| 3.3.34                 | VB_I2Sy                                |     |

| 3.3.35                 | <b>-</b>                               |     |

|                        | VB_SYNC                                |     |

| 3.3.36                 | UMTS_ON                                | 5/  |

# **CONFIDENTIAL**

| 3.3.37   | MP3                                                                 |      |

|----------|---------------------------------------------------------------------|------|

| 3.3.38   | SYNTH                                                               |      |

| 3.3.39   | RF_ADAPT                                                            |      |

| 3.3.40   | AUDIOPOSTPROC                                                       | . 60 |

| 3.3.41   | PCMPLAY                                                             |      |

| 3.3.42   | DTW                                                                 |      |

| 3.3.43   | TX_DIG                                                              |      |

| 3.3.44   | I2S_SWAP                                                            | . 62 |

| 4        | Modem Functions                                                     | . 63 |

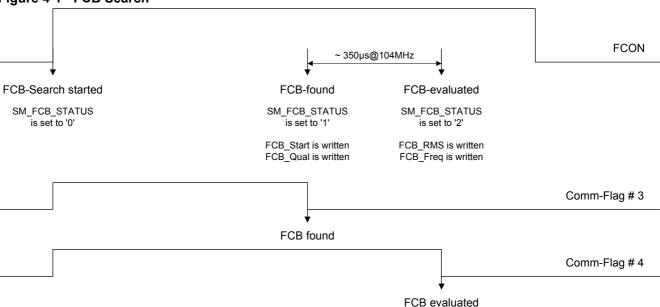

| 4.1      | FCB Search                                                          | . 63 |

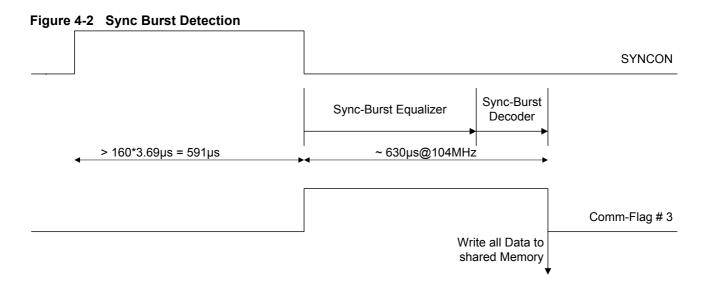

| 4.2      | Sync Burst Detection                                                | . 64 |

| 4.3      | Monitoring                                                          | . 65 |

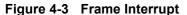

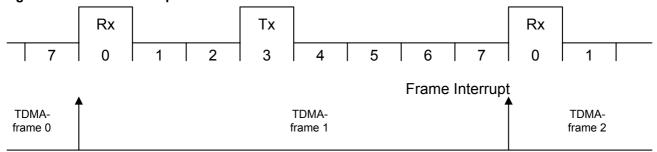

| 4.4      | Frame Interrupt                                                     | . 65 |

| 4.5      | TDMA Counters                                                       | . 66 |

| 4.6      | Equalizer                                                           | . 66 |

| 4.6.1    | Equalizer Output Parameters                                         | . 66 |

| 4.6.2    | Enhanced Measurement Reporting Support                              | . 68 |

| 4.7      | Modulator                                                           | . 69 |

| 4.7.1    | Analog Transmit Path                                                | . 69 |

| 4.7.2    | Digital Transmit Path                                               | . 69 |

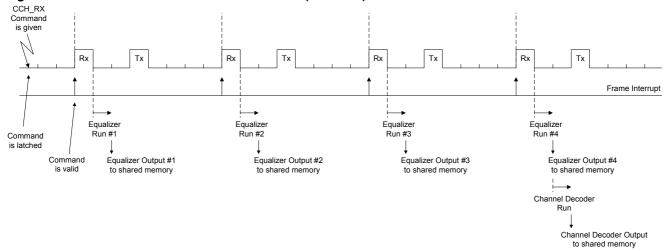

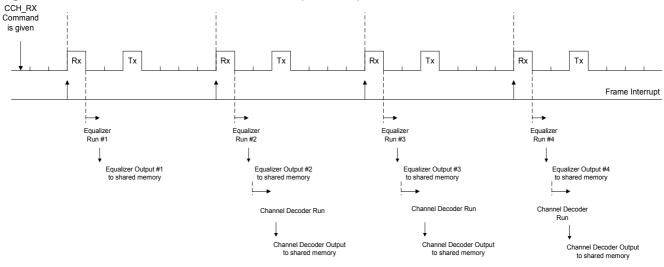

| 4.8      | Control Channel Receive on CCCH (Mode 51) or PCCCH                  | . 70 |

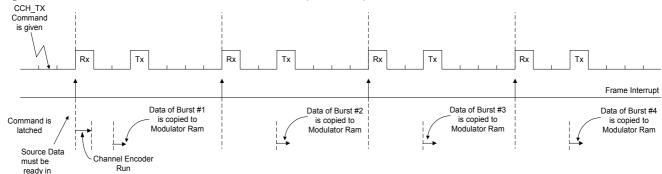

| 4.9      | Control Channel Transmit on CCCH (Mode-51) or PCCCH                 | . 71 |

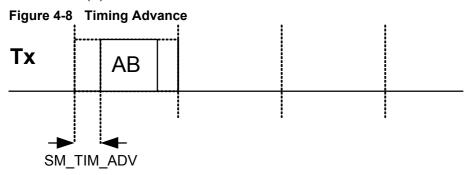

| 4.10     | Access Burst (RACH)                                                 | . 72 |

| 4.11     | TCH 26 Mode                                                         | . 73 |

| 4.11.1   | Sacch                                                               | . 74 |

| 4.11.2   | Facch                                                               | . 75 |

| 4.11.3   | Speech Channels                                                     | . 77 |

| 4.11.4   | AMR Channels (AFS and AHS)                                          | . 78 |

| 4.11.4.1 | Link Adaptation                                                     | . 78 |

| 4.11.4.2 | RATSCCH Messages                                                    | . 81 |

| 4.11.4.3 | Frame Types in AMR                                                  | . 82 |

| 4.11.4.4 | AMR DRX Flag                                                        | . 83 |

| 4.11.5   | Data Channels                                                       | . 83 |

| 4.12     | PDCH Mode                                                           | . 85 |

| 4.12.1   | Packet Idle Mode                                                    | . 86 |

| 4.12.1.1 | CCH_RX and CCH_TX                                                   | . 86 |

| 4.12.1.2 | PDCH Mode                                                           | . 86 |

| 4.12.2   | Packet Transfer Mode                                                | . 87 |

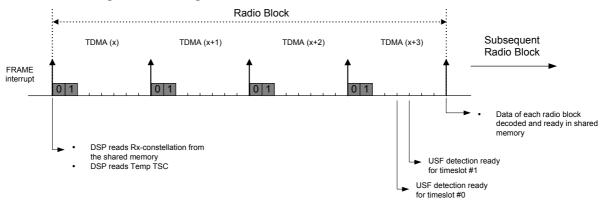

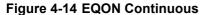

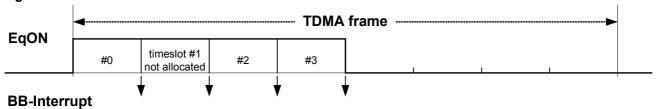

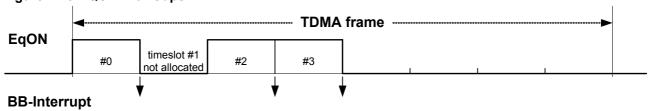

| 4.12.2.1 | Receiving Radio Blocks                                              | . 88 |

| 4.12.3   | PRACH                                                               | . 99 |

| 4.12.4   | PACCH                                                               | . 99 |

| 4.12.5   | PTCCH                                                               | 100  |

| 4.12.6   | Paging of Circuit Switched Services during PDCH Mode                | 101  |

| 5        | Voiceband Processing Functions                                      | 103  |

| 5.1      | Hardware Interfaces                                                 |      |

| 5.1.1    | Audio Front-End Interface (AFE) and External Audio Output (by I2S2) | 105  |

| 5.1.2    | I2Sx Interface                                                      |      |

| 5.1.3    | I2Sy Interface                                                      |      |

| 5.2      | Sample-Based Voiceband Processing                                   |      |

| 5.2.1    | Overview                                                            |      |

# **CONFIDENTIAL**

| 5.2.2   | Biquad Filters                                                                    | 109 |

|---------|-----------------------------------------------------------------------------------|-----|

| 5.2.3   | Tone Generator                                                                    | 109 |

| 5.2.4   | Sample-Based Sample Rate Converter                                                | 112 |

| 5.3     | Frame-Based Voiceband Processing                                                  | 112 |

| 5.3.1   | Overview                                                                          | 112 |

| 5.3.2   | Handsfree                                                                         | 114 |

| 5.3.3   | TTY/CTM                                                                           | 116 |

| 5.3.3.1 | TTY Signals                                                                       | 116 |

| 5.3.3.2 | CTM Signals                                                                       | 116 |

| 5.3.3.3 | Switching between Speech and Data                                                 | 117 |

| 5.3.4   | Voice Memo                                                                        | 117 |

| 5.3.4.1 | Data Interface                                                                    | 118 |

| 5.3.4.2 | Storage Format                                                                    | 119 |

| 5.3.4.3 | Voice Memo Use-Cases                                                              | 121 |

| 5.3.5   | DTW Speech Recognizer                                                             | 121 |

| 5.3.5.1 | Initialization                                                                    | 122 |

| 5.3.5.2 | Normalized Pattern Calculation                                                    |     |

| 5.3.5.3 | Calculation of Distance between Actual Normalized Pattern and a Reference Pattern |     |

| 5.3.5.4 | Adaptation of a Reference                                                         | 125 |

| 5.3.5.5 | DTW Speech Recognizer Use-Cases                                                   | 126 |

| 5.4     | Circular Mixing Buffer                                                            |     |

| 5.4.1   | Circular Mixing                                                                   |     |

| 5.4.2   | MP3                                                                               |     |

| 5.4.3   | Synthesizer                                                                       |     |

| 5.4.3.1 | Audio Postprocessing for Synthesizer                                              |     |

| 5.4.4   | I <sup>2</sup> S <sub>y</sub> External Mode                                       |     |

| 5.4.5   | PCM Player                                                                        |     |

| 5.4.5.1 | Interface to Controller                                                           |     |

| 5.4.5.2 | ADPCM Decoder                                                                     |     |

| 5.4.6   | Block-Based Sample Rate Converter                                                 |     |

| 5.5     | DAI Functions                                                                     | 134 |

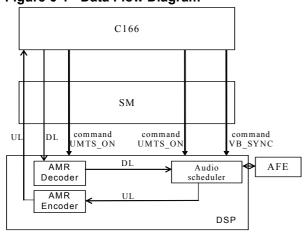

| 6       | UMTS Audio Interface                                                              | 139 |

| 6.1     | System Overview                                                                   | 139 |

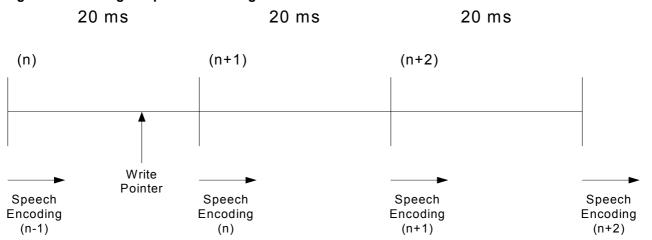

| 6.2     | UMTS Uplink                                                                       | 140 |

| 6.3     | UMTS Downlink                                                                     |     |

| 6.4     | Voiceband Synchronization                                                         | 141 |

| 6.4.1   | First Synchronization                                                             | 141 |

| 6.4.2   | Re-synchronization                                                                | 141 |

| 6.4.3   | Parameter Range                                                                   | 141 |

| 6.5     | Data Interface Format                                                             | 142 |

| 3.5.1   | Frame Types                                                                       | 143 |

| 6.5.2   | Frame Header                                                                      | 143 |

| 6.5.3   | Storage Format                                                                    | 144 |

| 7       | Shared Memory                                                                     | 149 |

| 7.1     | Contents of Shared Memory                                                         |     |

|         | •                                                                                 |     |

| B       | Run Times Of DSP Algorithms                                                       |     |

| 8.1     | Run Times Of DSP Algorithms                                                       | 154 |

| 9       | Document List and Glossary                                                        | 157 |

Firmware Manual 8 Rev. 1.01, 2005-12-07

### 1 Introduction

Attention: This document is valid starting from Startup Code G16 V1.3

| CONFIDEN Revision H |             | 2005-12-07                                              | Rev. 1.01 |

|---------------------|-------------|---------------------------------------------------------|-----------|

| Previous Ve         | ersion:     | Rev. 1.00, 2005-05-16                                   |           |

| Page                | Subjec      | ts (major changes since last revision)                  |           |

|                     | Initial \   | /ersion based on <i>E-GOLDradio G14 Firmware Manual</i> |           |

| Changes for         | or Rev. 1.0 | 1                                                       |           |

# Remarks on the Usage of This Document

- The digital signal processor is called TEAKlite or DSP. The microcontroller is called MCU.

- All references to shared memory locations are made in code-style letters like SM\_BOOT\_DATA. All names for

these shared memory locations have the sequence "SM\_.." as their leading letters. The exact position and

size of these shared memory locations can be read from Section 7.1 "Contents of Shared Memory" on

Page 149.

- The bitstream in a shared memory block always has the same order. The first bit of the bitstream is in the first word at bit position '0' (LSB). The second bit is at bit position '1'. The 17th bit is located in the second word at bit position '0' and so on.

- All RMS values in this document are given in [dB/16]. Therefore, if the signal level is reduced to 50% (6 dB) the corresponding RMS value is decreased by  $6*16 = 96_D$ . The maximum value that can be reached with a full scale signal in the baseband buffer is about  $1400_D$ .

- All metric references in this document (SM\_SYNC\_METRIC, SM\_TCH\_METRIC, etc.) are output values of the

Viterbi-Algorithm in the Channel-Decoder. These values indicate how many bits have been corrected by the

Viterbi-Algorithm. Therefore, a metric value of '0' means that no bits have been corrected, a value of n means

that n bits have been corrected. The maximum value of n depends on the channel type (for example, <= 78 for

Synch Bursts, <= 378 for Full Speech).</li>

Note: The Infineon interfaces contain links to MP3 algorithms, which are proprietary to the Fraunhofer Gesellschaft. Infineon does not grant any license or right to use MP3. For detailed information about MP3 or the right to use such Intellugale Property, please contact the Fraunhofer Gesellschaft directly.

#### 1.1 Overview

The E-GOLDradio DSP subsystem consists of a 16-bit TEAKlite core (running at 104MHz) and hardware peripherals. It is a coprocessor for the MCU. On the DSP, there are algorithms and an operating system called the scheduler.

Firmware Manual 9 Rev. 1.01, 2005-12-07

# 1.2 Algorithm Partitioning

The signal processing algorithms listed below are implemented in Firmware modules. These modules are in a 80 k-word program ROM and a 4 k-word program RAM:

- Scanning of channels for measurement of field strengths of neighboring base stations

- Detection and evaluation of Frequency Correction Bursts

- Equalization of GMSK Normal Bursts and Synchronization Bursts with bit-by-bit soft-output

- Synch burst channel decoder

- Channel encoding and soft-decision decoding for fullrate, enhanced-fullrate, halfrate, and AMR speech

- Support for fullrate (F14.4, F9.6, F4.8, and F2.4) and halfrate (H2.4 and H4.8) data channels

- Control channels as well as Rach and Prach

- GPRS coding schemes (CS1-CS4)

- Fast USF detection algorithms for the Medium Access Control (MAC) software layer

- Fullrate, enhanced fullrate, and halfrate speech encoding and decoding

- Adaptive multi-rate (fullrate and halfrate) speech encoding and decoding

- Mandatory sub-functions such as:

- Discontinuous transmission, DTX (GSM 46.031, 46.041, 46.081, and 46.093 standards)

- Voice activity detection, VAD (GSM 46.032, 46.042, 46.082, and 46.094 standards)

- Background noise calculation (GSM 46.012, 46.022, 46.062, and 46.092 standards)

- · Generation of tone and side tone

- Hands-free function

- Support for voice memo

- Handling of vocoder and voice-paths for type approval testing

- Synthesizer with up to 40 voices at 16 kHz sampling rate and 21 voices at 32 kHz.

- TTY/CTM converter

- PCM/ADPCM Player

- MP3 Player (optional).

#### 1.3 Scheduler Functions

The scheduler is based on an operating system and is triggered by interrupts generated by hardware peripherals or commands from the MCU.

The scheduler features:

- · Communications between DSP and MCU

- · Semi-automatic handling of control channels

- Fully automatic handling of speech and data traffic channels

- Support of the GSM ciphering algorithms (A51, A52, and A53) in combination with a hardware accelerator

- Support for High Speed Circuit Switched Data (HSCSD) with a maximum of 4 RX and 1 TX or 3 RX and 2 TX timeslots (Class 10 mobile)

- Support for General Packet Radio Services GPRS with up to 4 RX and 1 TX or 1 RX and 4 TX (Class 12 mobile).

Note: The E-GOLDradio GPRS Class depends on the MCU workload.

- Monitoring of paging blocks for packet switched and circuit switched services simultaneously (GPRS MS in Class-B mode of operation)

- Loop-back functions (according to GSM 11.10 standard)

- Audio scheduler that supports various sample rates (including handling of MP3, Synthesizer, TTY/CTM, PCM/ADPCM player, and echo cancellation algorithms)

- Voice Memo for Full Rate Speech and AMR.

Firmware Manual 10 Rev. 1.01, 2005-12-07

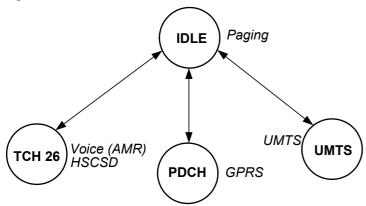

For the modem the scheduler has four states:

- 1. IDLE State:

- Receiving and transmitting frames that do not belong to a circuit or packet switched channel

- Receiving paging channels and broadcast channels on the 51 multiframe.

- 2. TCH26 State:

- Speech circuit switched services with narrowband AMR

- Data services and HSCSD (By-Pass-Mode).

- 3. PDCH State:

- GPRS packet switched services.

- 4. UMTS State:

- Only speech processing support for an external UMTS modem processor.

The transition from one state to another can only be forced by the MCU. As it is shown in **Figure 1-1** the transition between the states TCH26, UMTS, and PDCH can only be made by going through IDLE state.

Figure 1-1 Firmware States

The DSP modem functions belong to all four states: DSP IDLE, TCH26, PDCH, UMTS.

Firmware Manual 11 Rev. 1.01, 2005-12-07

Table 1-1 shows the applications that can be used during each of the four DSP states.

Table 1-1 Usable Applications during the Different FW States at 104 MHz

| DSP Status                                            | Voiceband Processing Functions (Applications) |                                           |                                           |         |               |         |                                                                         |               |  |

|-------------------------------------------------------|-----------------------------------------------|-------------------------------------------|-------------------------------------------|---------|---------------|---------|-------------------------------------------------------------------------|---------------|--|

| (Modem<br>Functions)                                  | Internal<br>Voice<br>Memo                     | Number of<br>Synthesizer<br>Voices/16 kHz | Number of<br>Synthesizer<br>Voices/32 kHz | МР3     | Hands<br>free | TTY-CTM | I <sup>2</sup> S <sub>y</sub><br>external<br>Mode<br>Circular<br>Buffer | PCM<br>Player |  |

| Idle                                                  | yes                                           | 40                                        | 21                                        | yes     | -             | -       | yes                                                                     | yes           |  |

| Tch26 Signal<br>Only                                  | yes                                           | 32                                        | 17                                        | yes     | -             | -       | yes                                                                     | yes           |  |

| Tch26 Data<br>Services<br>Single Slot                 | yes                                           | -                                         | -                                         | -       | -             | -       | yes                                                                     | yes           |  |

| Tch26<br>HSCSD                                        | -                                             | -                                         | -                                         | -       | -             | -       | yes                                                                     | yes           |  |

| Tch26 Voice<br>(Speech<br>Calls such as<br>AMR, etc.) | yes                                           | -                                         | -                                         | -       | yes           | yes     | yes                                                                     | yes           |  |

| PDCH GPRS                                             | yes                                           | 14                                        | 7                                         | Class 9 | -             | -       | yes                                                                     | yes           |  |

| UMTS                                                  | yes                                           | -                                         | -                                         | -       | yes           | -       | yes                                                                     | yes           |  |

Table 1-2 Combination of Audio Applications

| Audio Application   | I2Sy_MMS | l2Sy_External | Synthesizer | PCM Player | Internal Voice<br>Memo | Handsfree | TTY/CTM | Tone Generator |

|---------------------|----------|---------------|-------------|------------|------------------------|-----------|---------|----------------|

| I2Sy_MMS            |          | no            | yes         | yes        | yes                    | yes       | yes     | yes            |

| I2Sy_External       | no       |               | no          | no         | yes                    | yes       | yes     | yes            |

| Synthesizer         | yes      | no            |             | no         | no                     | no        | yes     | yes            |

| PCM Player          | yes      | no            | no          |            | yes                    | yes       | no      | yes            |

| Internal Voice Memo | yes      | yes           | no          | yes        |                        | no        | no      | yes            |

| Handsfree           | yes      | yes           | no          | yes        | no                     |           | no      | yes            |

| TTY/CTM             | yes      | yes           | yes         | no         | no                     | no        |         | yes            |

| Tone Generator      | yes      | yes           | yes         | yes        | yes                    | yes       | yes     |                |

#### Notes:

- 1. Modem related applications like Frequency Correction, SynchBurst and Monitoring always work in parallel.

- 2. The Audio Scheduler for 8 kHz must be started for every application!

- 3. The use of the Audio Scheduler for 16 kHz is only allowed in the Idle-mode. The Internal Voice Memo at 16 kHz is not possible.

Firmware Manual 12 Rev. 1.01, 2005-12-07

# 2 Booting

| dio<br>NTIAL<br>History: 2005-12-07                      | Rev. 1.01                                                                                                                                                            |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ersion: Rev. 1.00, 2005-05-16                            |                                                                                                                                                                      |

| Subjects (major changes since last revision)             |                                                                                                                                                                      |

| Initial Version based on E-GOLDradio G14 Firmware Manual |                                                                                                                                                                      |

| for Rev. 1.01                                            |                                                                                                                                                                      |

|                                                          |                                                                                                                                                                      |

| ,                                                        | NTIAL History: 2005-12-07 ersion: Rev. 1.00, 2005-05-16 Subjects (major changes since last revision) Initial Version based on <i>E-GOLDradio G14 Firmware Manual</i> |

# 2.1 Boot Concept

After Reset, the startup code for the DSP has to be booted: the program RAM (and, if needed, some parts of the data RAM) has to be downloaded from the MCU. The data is written by the MCU to the shared memory and read by the DSP from the shared memory to the DSP-internal memory (for details on the shared memory refer to **Chapter 7 Shared Memory**).

Two different boot options are supported by the DSP:

- 1. Normal Boot procedure

- 2. Fast Boot procedure used after the Standby Power Down mode.

The following Boot Commands are available:

PLOAD: Load program RAM

DLOAD: Load data RAM

• BRANCH: Branch to a specific address

FAST: Fast Boot process after Standby Power Down

PREAD: Read from program address space

DREAD: Read from data address space.

Note: The commands listed in Section 3.2 "List of Commands" on Page 21 can NOT be applied before the DSP has been completely booted by the MCU. Only the boot commands listed above are allowed during this phase.

Note: After booting the startup-code, the MCU can use the shared memory locations SM\_FW\_VERSION and SM\_HW\_VERSION for other things, refer to Section 7.1 "Contents of Shared Memory" on Page 149. (If an error causes the DSP to reset, the first thing to do is verify that the correct versions of the Firmware and Hardware are being used by reading these two shared memory locations.)

Firmware Manual 13 Rev. 1.01, 2005-12-07

## 2.2 Normal Boot Procedure

This procedure is used for the first boot process of the DSP. During this process the DSP obtains the startup code from the MCU.

The following steps are done during the boot phase of the DSP:

- 1. Immediately after reset the DSP sets communication flag #0 to '1' to indicate to the MCU that the DSP is not ready to receive the first boot command.

- 2. After having some internal initialization (~2-3μs) the DSP resets communication flag #0 to '0' to indicate to the MCU that the DSP is ready to receive the first boot command.

- 3. The MCU may read the shared memory locations **SM\_FW\_VERSION** and **SM\_HW\_VERSION** to check the firmware version and the hardware version of the DSP-subsystem.

- 4. The MCU fills up the shared memory at address **SM\_BOOT\_DATA** with data belonging to the first boot command.

- 5. The MCU sets communication flag #0 to '1' and activate interrupt line #0 to the DSP. When this interrupt is received, the DSP starts accepting the boot command.

- 6. The MCU waits until the DSP has accepted the boot command by polling communication flag #0: as soon as the DSP has completely accepted the boot command it resets communication flag #0 to '0' again.

- 7. If this is not the last boot command (BRANCH), the MCU fills up the shared memory at address **SM\_BOOT\_DATA** with data belonging to the next boot command. Go back to step **5**.

The boot commands PLOAD and DLOAD, program and data RAM respectively, can be loaded. These commands can be called several times to load different parts of program RAM and data RAM. After loading all the necessary program RAM and data RAM locations, the command BRANCH has to be given to force DSP out of the boot loop to start normal program flow. The BRANCH command is always the last boot command.

Note: When the branch command is acknowledged by the DSP this guarantees that the DSP is ready to receive the first command (refer to Section 3.2 "List of Commands" on Page 21) from the MCU. This means that the DSP Firmware is completely initialized.

Firmware Manual 14 Rev. 1.01, 2005-12-07

To give a boot command, the shared memory, starting at offset SM\_BOOT\_DATA, has to be filled as indicated in Table 2-1

Table 2-1 Load Boot commands

| Shared Memory address | Boot Command PLOAD       | Boot Command DLOAD       | Boot Command<br>BRANCH |

|-----------------------|--------------------------|--------------------------|------------------------|

| SM_BOOT_DATA          | 0                        | 1                        | 2                      |

| SM_BOOT_DATA+1        | P-RAM Destination        | D-RAM Destination        | Branch-Address         |

| SM_BOOT_DATA+2        | Block-Length1            | Block-Length2            |                        |

| SM_BOOT_DATA+3        | Data-Word #1             | Data-Word #1             |                        |

| SM_BOOT_DATA+4        | Data-Word #2             | Data-Word #2             |                        |

|                       |                          |                          |                        |

| SM_BOOT_DATA+         |                          | Data-Word #Block-Length2 |                        |

| Block_Length2+2       |                          |                          |                        |

|                       |                          |                          | •                      |

| SM_BOOT_DATA+         | Data-Word #Block-Length1 |                          |                        |

| Block_Length1+2       |                          |                          |                        |

Note: The maximum block-length for downloading program or data memory is limited to 507 (512-2-3) words.

Table 2-2 Read Boot commands

| Shared Memory address | Boot Command PREAD | Boot Command DREAD | Boot Command FAST |

|-----------------------|--------------------|--------------------|-------------------|

| SM_BOOT_DATA          | 3                  | 4                  | 5                 |

| SM_BOOT_DATA+1        | P-Space<br>Source  | D-Space<br>Source  |                   |

| SM_BOOT_DATA+2        | Block-Length       | Block-Length       |                   |

Note: The maximum block-length for reading program or data memory is (512-2-3) words. On exit of the PREAD and DREAD commands the read data are located in shared memory beginning at SM\_BOOT\_DATA+3 and ending at SM\_BOOT\_DATA+Block\_Length+2.

Firmware Manual 15 Rev. 1.01, 2005-12-07

#### 2.3 Fast Boot Procedure

This procedure wakes up the DSP from the Standby Power Down mode where the DSP and all peripherals are switched off. The shared memory that is switched on during the Standby Power Down must contain the startup code.

The Standby Power Down mode can be forced by applying the command **PW\_DOWN**. The wake-up procedure is similar to the normal BOOT procedure. Only two MCU commands are necessary to wake-up the DSP:

- 1. Immediately after reset the DSP sets communication flag #0 to '1' to indicate to the MCU that the DSP is not yet ready to receive the first boot command.

- 2. After some internal initialization ( $\sim$ 2-3 $\mu$ s), the DSP resets communication flag #0 to '0' to indicate to the MCU that the DSP is ready to receive the first boot command.

- 3. The DSP quickly restores the data from the shared memory by giving the command FAST. In the worst case, the DSP needs 6000 cycles for 1 kwords. For applying the FAST command, the MCU must set communication flag #0 to '1' and activate interrupt #0 to the DSP. Receiving this interrupt, the DSP starts accepting the FAST command.

- 4. After having finished the fast FAST-command, the DSP resets communication flag #0 and is now ready for the next command.

- 5. The MCU gives the BRANCH command.

The shared memory locations SM\_SBPD\_INFO and SM\_SBPD\_BOOT\_ADD contain the Standby Power Down (SBPD) related data. Under all circumstances, it must be guaranteed that MCU does not overwrite those shared memory locations in the time period between giving the PW\_DOWN command and the end of the fast boot procedure.

This SBPD support can only be used if the size of the Data and Program Code of the Startup Code does not exceed the size of the Shared Memory Field **SM\_SBPD\_BOOT\_ADD**.

Note: The Firmware Group does not guarantee that this requirement is fulfilled for startup codes after startup version 1.0.

#### 2.4 Firmware ID and DSP Subsystem ID

Table 2-3 Version Information Locations in SM

| PMB 7870-Version  | SM_FW_VERSION     | SM_HW_VERSION     | SCU_CHIPID.CHREV |

|-------------------|-------------------|-------------------|------------------|

| PMB 7870 V1.0 G14 | 0604 <sub>H</sub> | E001 <sub>H</sub> | 07 <sub>H</sub>  |

| PMB 7870 V1.0 G16 | 0606 <sub>H</sub> | E001 <sub>H</sub> | 07 <sub>H</sub>  |

The Firmware Mask version can be read from the Shared Memory location **SM\_FW\_VERSION** that is used for the PMR 7870 V1 v

The hardware DSP Subsystem version can be read from the Shared Memory location **SM\_HW\_VERSION** that is used for the PMB 7870 V1.x.

The Chip Revision Number can be read from the chip identification bit field **SCU\_CHIPID.CHREV**. For more information, refer to the *E-GOLDradio Design Specification*.

# 2.5 Startup-Code Version

From Startup-Code 1.0.0 the information about the Startup-Code version is written to the shared memory location **SM\_STARTUP\_CODE\_VERSION**. The version number has three parts:

Startup-code version: This number starts from 1 and is increased for major changes (for example, feature

extension, interface change, etc.). When this number is increased the other parts of the version number have

to be reset to zero.

Firmware Manual 16 Rev. 1.01, 2005-12-07

2. Startup-code subversion: This number starts from 0 and is increased for non-major changes (changes that are not covered by part 1). When this number is increased the third part of the version number has to be reset to zero.

3. Debug-code version: This number starts from 0 (for the official release) and is increased for every debug patch based for the current release.

**Table 2-4** shows the location of the different parts in **SM\_STARTUP\_CODE\_VERSION**.

Table 2-4 Bit ordering in SM\_STARTUP\_CODE\_VERSION

| Bit Number | Bit15Bit12           | Bit11Bit14               | Bit3Bit0           |

|------------|----------------------|--------------------------|--------------------|

| Part       | 1                    | 2                        | 3                  |

| Name       | Startup-Code Version | Startup-Code Sub-version | Debug-Code Version |

| Example    | 1                    | 5                        | 0                  |

Firmware Manual 17 Rev. 1.01, 2005-12-07

**Booting**

# 3 Commands

| E-GOLDradio<br>CONFIDENT<br>Revision His | AL                                | Rev. 1.01                                                        |  |

|------------------------------------------|-----------------------------------|------------------------------------------------------------------|--|

| Previous Vers                            | ion: Rev. 1.00, 2005-05-16        | 6                                                                |  |

| Page                                     | Subjects (major changes since las | ast revision)                                                    |  |

|                                          | Initial Version based on E-GOLDr  | radio G14 Firmware Manual                                        |  |

| Changes for                              | Rev. 1.01                         |                                                                  |  |

| Page 32                                  | Update number of user command     | ds                                                               |  |

| Page 23                                  | Add command parameter descrip     | otion for external audio output by I <sup>2</sup> S <sub>2</sub> |  |

| Page 32                                  | Modify default value of the TX_DI | IG command                                                       |  |

# 3.1 DSP Subsystem Command Interface to MCU

Commands are used to give the MCU control over the DSP. For example, the MCU can order the DSP to switch on or off DTX-mode or start a new traffic channel.

Commands are given via interrupts. The MCU writes parameters to a command block in the shared memory and give an interrupt to the DSP. After having received this interrupt the DSP will read the command block and interpret it.

There are three command pipes. Each of them has a separate interrupt line from the MCU to the DSP and its own command block in the shared memory. These three command pipes use the bits #0, #1, and #2 of register **SCU\_MCUTODSP** to send an interrupt from the MCU to the DSP and the MCU must load the appropriate parameters into the shared memory locations **SM\_MCU\_CMD\_0**, **SM\_MCU\_CMD\_1**, and **SM\_MCU\_CMD\_2**.

The three command pipes are orthogonal. This means that any command may be given via any of the command pipes #0, #1, and #2.

At the DSP all three command pipes have higher interrupt priority than all the other interrupts (except CODONHI, BBHI and I2S2RX by default or I2S1RX), but command pipe #0 has higher priority than command pipe #1, and command pipe #1 has higher priority than command pipe #2. This does not mean that command pipe #1 may interrupt command pipe #0; it means that, if pipe #0 and pipe #1 are active at the same time, pipe #0 will be served first.

Firmware Manual 19 Rev. 1.01, 2005-12-07

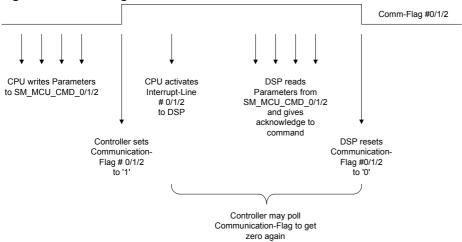

A command is given in same way a boot command (boot commands are allowed in the boot phase only). The following steps have to be done (see **Figure 3-1**):

- The MCU has to write the command code and the command parameters to the shared memory. This means

that the command code has to be written to the location <u>sm\_mcu\_cmd\_0</u>, <u>sm\_mcu\_cmd\_1</u>, or

<u>sm\_mcu\_cmd\_2</u>, and the command parameters have to follow at the addresses <u>sm\_mcu\_cmd\_0/1/2+1</u>,

<u>sm\_mcu\_cmd\_0/1/2+2</u>, etc.

- The MCU sets communication flag #0, #1 or #2 to '1' and activates interrupt #0, #1 or #2 using register SCU\_MCUTODSP. Upon receiving this interrupt the DSP starts accepting the command on the corresponding pipe.

- 3. After sending this interrupt the MCU waits until the DSP has accepted the command. This is done by (periodically) polling the communication flags because as soon as the DSP has accepted the command it will reset the communication flag to '0' again.

- 4. If the command has been accepted correctly, a value of "negative command number#" is returned by the DSP in the corresponding shared memory location SM\_MCU\_CMD\_0, SM\_MCU\_CMD\_1 or SM\_MCU\_CMD\_2. If the command failed, a value of '0' is returned.

Figure 3-1 Sending a Command from MCU to DSP

The procedure for the MCU to apply a command is always the same as described above, but the DSP distinguishes between two different types of commands:

1. Asynchronous commands

These commands are valid immediately after acceptance by the DSP. These are most commands are of this type.

2. Synchronous commands

These commands are accepted immediately, but do not become valid before the next frame interrupt. Only few commands belong to this type: CCH\_RX, CCH\_TX, TCH\_26, and PDCH.

Note: The DSP subsystem guarantees that each command sent by the MCU is accepted within 70us.

Firmware Manual 20 Rev. 1.01, 2005-12-07

# 3.2 List of Commands

**Table 3-1** is the list of commands. A detailed description of these commands is given in **Section 3.3 "Command Description" on Page 33**..

Table 3-1 List of commands

| Name      | Command Number | Operation Description                                  |  |

|-----------|----------------|--------------------------------------------------------|--|

|           | Parameters     | Parameter Descriptions                                 |  |

| FC_INIT   | 1              | Initialization for FCB Search                          |  |

|           | MODE           | 0: Stand-By                                            |  |

|           |                | 1: Traffic                                             |  |

|           | THRSH          | Threshold value                                        |  |

|           | HYST           | Hysteresis Value                                       |  |

| MODU_INIT | 2              | Initialization for Modulator                           |  |

|           | IOFFS          | I-Offset Pre-Correction for the GMSK Modulator         |  |

|           | QOFFS          | Q-Offset Pre-Correction for the GMSK Modulator         |  |

|           | IAMP           | I-Amplitude Pre-Correction for the GMSK Modulator      |  |

|           | QAMP           | Q-Amplitude Pre-Correction for the GMSK Modulator      |  |

|           | GMSK_<br>FREQ  | Frequency Pre-Correction for the GMSK Modulator        |  |

|           | DUMMY          | Additional number of dummy bits for the GMSK Modulator |  |

|           | IQ_SETUP       | Additional IQ Swap for the GMSK Modulator              |  |

| IQ_SWAP_1 | 3              | IQ-Swap for GMSK Normal Burst Rx and Tx                |  |

|           | SWITCH         | 0: IQ-Swap is off                                      |  |

|           |                | 1: IQ-Swap is on                                       |  |

| IQ_SWAP_2 | 4              | IQ-Swap for FCB-Search and Sync Burst Detection        |  |

|           | SWITCH         | 0: IQ-Swap is off                                      |  |

|           |                | 1: IQ-Swap is on                                       |  |

| DEC_INIT  | 5              | Initialization for Channel Decoder                     |  |

| _         | SWITCH         | CODEC Switch                                           |  |

|           |                | 0: Full Rate Speech (FS)                               |  |

|           |                | 1: Enhance Full Rate Speech (EFR)                      |  |

|           |                | 2: Half Rate Speech (HS)                               |  |

|           |                | 3: Adaptive Multi Rate (AMR)                           |  |

|           | PAR 0 - 25     | Number of parameters depends on SWITCH                 |  |

|           |                |                                                        |  |

Table 3-1 List of commands

| Name          | Command Number                                                          | Operation Description                                                                                                                                                                                 |  |  |

|---------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               | Parameters                                                              | Parameter Descriptions                                                                                                                                                                                |  |  |

| CIPH_KEY      | 6                                                                       | Set Cipher Mode and/or Cipher Keys                                                                                                                                                                    |  |  |

|               | SWITCH                                                                  | 1: Set Cipher Mode only                                                                                                                                                                               |  |  |

|               |                                                                         | 2: Set Cipher Keys only                                                                                                                                                                               |  |  |

|               |                                                                         | 3: Set both Cipher Mode and Cipher Keys                                                                                                                                                               |  |  |

|               | CIPH                                                                    | Ciphering: Off/A51/A52/A53                                                                                                                                                                            |  |  |

|               | SS                                                                      | Sub-Stream Number                                                                                                                                                                                     |  |  |

|               | CKEY0                                                                   | Cipher Key 0                                                                                                                                                                                          |  |  |

|               | CKEY1                                                                   | Cipher Key 1                                                                                                                                                                                          |  |  |

|               | CKEY2                                                                   | Cipher Key 2                                                                                                                                                                                          |  |  |

|               | CKEY3                                                                   | Cipher Key 3                                                                                                                                                                                          |  |  |

|               | CKEY4                                                                   | Cipher Key 4 for A53, otherwise same as Cipher Key 0                                                                                                                                                  |  |  |

|               | CKEY5                                                                   | Cipher Key 5 for A53, otherwise same as Cipher Key 1                                                                                                                                                  |  |  |

|               | CKEY6                                                                   | Cipher Key 6 for A53, otherwise same as Cipher Key 2                                                                                                                                                  |  |  |

|               | CKEY7                                                                   | Cipher Key 7 for A53, otherwise same as Cipher Key 3                                                                                                                                                  |  |  |

|               |                                                                         |                                                                                                                                                                                                       |  |  |

| CCH_RX        | 7                                                                       | Receive Control Channel                                                                                                                                                                               |  |  |

|               | CIPH                                                                    | Ciphering: don't change/Off/A51/A52/A53                                                                                                                                                               |  |  |

|               | TSC                                                                     | Training Sequence Number                                                                                                                                                                              |  |  |

|               | EARLY                                                                   | Defines channel decoding mode:                                                                                                                                                                        |  |  |

|               |                                                                         | 0: After receiving complete data frame (4 bursts)                                                                                                                                                     |  |  |

|               |                                                                         | 1: After receiving partial frame (only 2 or 3 bursts)                                                                                                                                                 |  |  |

|               |                                                                         |                                                                                                                                                                                                       |  |  |

|               |                                                                         |                                                                                                                                                                                                       |  |  |

| ССН_ТХ        | 8                                                                       | Transmit Control Channel                                                                                                                                                                              |  |  |

| ссн_тх        | 8<br>CIPH                                                               | Transmit Control Channel Ciphering: do not change/Off/A51/A52/A53                                                                                                                                     |  |  |

| ссн_тх        |                                                                         |                                                                                                                                                                                                       |  |  |

| ссн_тх        | CIPH                                                                    | Ciphering: do not change/Off/A51/A52/A53                                                                                                                                                              |  |  |

| _             | CIPH                                                                    | Ciphering: do not change/Off/A51/A52/A53                                                                                                                                                              |  |  |

| _             | CIPH<br>TSC                                                             | Ciphering: do not change/Off/A51/A52/A53 Training Sequence Number                                                                                                                                     |  |  |

| CCH_TX TCH_26 | CIPH<br>TSC                                                             | Ciphering: do not change/Off/A51/A52/A53  Training Sequence Number  Start (or modify) TCH-26 Channel                                                                                                  |  |  |

| _             | CIPH<br>TSC<br>9<br>CHT                                                 | Ciphering: do not change/Off/A51/A52/A53 Training Sequence Number  Start (or modify) TCH-26 Channel Channel Type                                                                                      |  |  |

| _             | CIPH<br>TSC<br>9<br>CHT<br>CIPH                                         | Ciphering: do not change/Off/A51/A52/A53  Training Sequence Number  Start (or modify) TCH-26 Channel  Channel Type  Ciphering: don't change/Off/A51/A52/A53  Training Sequence Number                 |  |  |

|               | CIPH TSC  9 CHT CIPH TSC                                                | Ciphering: do not change/Off/A51/A52/A53 Training Sequence Number  Start (or modify) TCH-26 Channel Channel Type Ciphering: don't change/Off/A51/A52/A53 Training Sequence Number Initialization Flag |  |  |

|               | CIPH TSC  9 CHT CIPH TSC INIT PAR1                                      | Ciphering: do not change/Off/A51/A52/A53 Training Sequence Number  Start (or modify) TCH-26 Channel Channel Type Ciphering: don't change/Off/A51/A52/A53 Training Sequence Number Initialization Flag |  |  |

| _             | CIPH TSC  9 CHT CIPH TSC INIT PAR1 PAR2                                 | Ciphering: do not change/Off/A51/A52/A53 Training Sequence Number  Start (or modify) TCH-26 Channel Channel Type Ciphering: don't change/Off/A51/A52/A53 Training Sequence Number Initialization Flag |  |  |

| _             | CIPH TSC  9 CHT CIPH TSC INIT PAR1 PAR2 PAR3                            | Ciphering: do not change/Off/A51/A52/A53 Training Sequence Number  Start (or modify) TCH-26 Channel Channel Type Ciphering: don't change/Off/A51/A52/A53 Training Sequence Number Initialization Flag |  |  |

| _             | 9<br>CHT<br>CIPH<br>TSC<br>INIT<br>PAR1<br>PAR2<br>PAR3<br>PAR4         | Ciphering: do not change/Off/A51/A52/A53 Training Sequence Number  Start (or modify) TCH-26 Channel Channel Type Ciphering: don't change/Off/A51/A52/A53 Training Sequence Number Initialization Flag |  |  |

| _             | 9<br>CHT<br>CIPH<br>TSC<br>INIT<br>PAR1<br>PAR2<br>PAR3<br>PAR4<br>PAR5 | Ciphering: do not change/Off/A51/A52/A53 Training Sequence Number  Start (or modify) TCH-26 Channel Channel Type Ciphering: don't change/Off/A51/A52/A53 Training Sequence Number Initialization Flag |  |  |

| _             | 9<br>CHT<br>CIPH<br>TSC<br>INIT<br>PAR1<br>PAR2<br>PAR3<br>PAR4         | Ciphering: do not change/Off/A51/A52/A53  Training Sequence Number  Start (or modify) TCH-26 Channel  Channel Type  Ciphering: don't change/Off/A51/A52/A53  Training Sequence Number                 |  |  |

Table 3-1 List of commands

| Name   | Command<br>Number | Operation Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|--------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | Parameters        | Parameter Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| LOOP   | 10                | Close and Open Loops for circuit switch TCH26 connections (FR, HR, EFR, AMR and data services)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|        | SWITCH            | <ol> <li>Open Loop</li> <li>Signalling FER         <i>TCH Loop including signalling of erased frames</i> (Loop A)</li> <li>No Signalling FER         <i>Speech TCH loop without signalling of erased frames</i> (Loop B).</li> <li>Signalling erased and unreliable frames (HS only)         <i>TCH loop including Signalling erased and unreliable</i> frames (Loop D)</li> <li>Signalling erased SID frames (HS only)         <i>TCH loop including Signalling erased SID frames</i> (Loop E)</li> <li>Signalling erased valid SID frames (HS only)         <i>TCH Loop including Signalling erased valid SID frames</i> (Loop F)</li> <li><i>TCH Burst-by-Burst Loop</i> (Loop C)</li> <li><i>TCH Loop without signalling of erased frames for</i> in-band channel error rate (Loop I) (AMR only)</li> </ol> |  |  |

|        | UL-SRC#0          | Source for Uplink Substream #0 (0 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|        | UL-SRC#1          | Source for Uplink Substream #1 (0 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| PDCH   | 11                | Start or modify the Packet Data Channel (PDCH) mode (only in the first TDMA frame of a radio block)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|        | TSC               | Training Sequence Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|        | MODE              | 0 = GPRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| BB_OFF | 13                | Leave Modem related algorithms and go to Idle state (Audio unaffected). Refer to Section 3.3.12 "BB_OFF" on Page 46.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| IDLE   | 14                | Same as command <b>BB_OFF</b> . Additionally all algorithms running a stopped and go to Idle state. The Audio scheduler sample based not influenced. Refer to <b>Section 3.3.13 "IDLE" on Page 48</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| VB_ON  | 15                | Configuration of the $I^2S_x$ interface and the AFE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

Table 3-1 List of commands

| Table 3-1 List of co | mmands         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                 | Command Number | Operation Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      | Parameters     | Parameter Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                      | SWITCH         | <ol> <li>Switch AFE off and I<sup>2</sup>S<sub>x</sub> off</li> <li>Copy parameters VRXCTRL1, VRXCTRL2, and VTXCTRL to AFE hardware.</li> <li>Switch AFE in/out on. Switch I<sup>2</sup>S<sub>x</sub> off.</li> <li>Switch I<sup>2</sup>S<sub>x</sub> on and AFE off.</li> <li>Switch I<sup>2</sup>S<sub>x</sub> on and AFE out on.</li> <li>Switch I<sup>2</sup>S<sub>x</sub> on, AFE in on, and AFE out off</li> <li>Switch I<sup>2</sup>S<sub>x</sub> on, AFE in on, and AFE out on</li> <li>Copy parameters VRXCTRL1, VRXCTRL2, VTXCTRL, and OUT_MODE to AFE hardware</li> <li>Switch I<sup>2</sup>S<sub>2</sub> on for external audio output, AFE in on, and AFE out off</li> </ol> |

|                      | VRXCTRL1       | 9: Switch I <sup>2</sup> S <sub>2</sub> on for external audio output, AFE in and out on.  Receive Control 1 register same as hardware register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      |                | AFE_VRXCTRL1, refer to [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                      | VRXCTRL2       | Receive Control 2 register same as hardware register AFE_VRXCTRL2, refer to [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

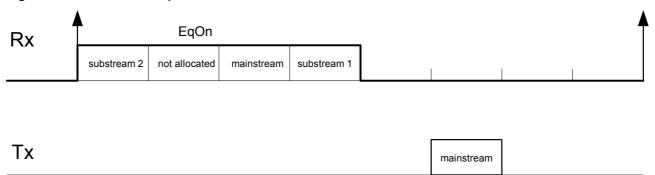

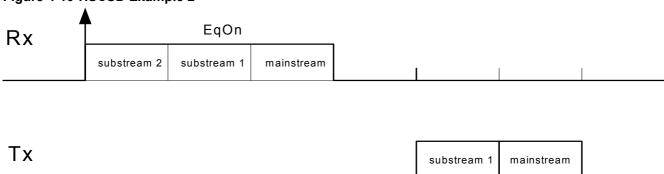

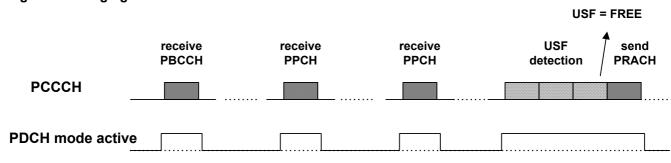

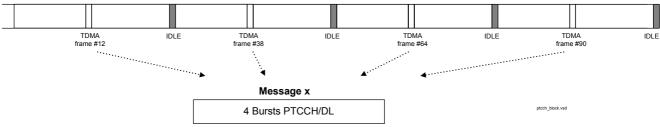

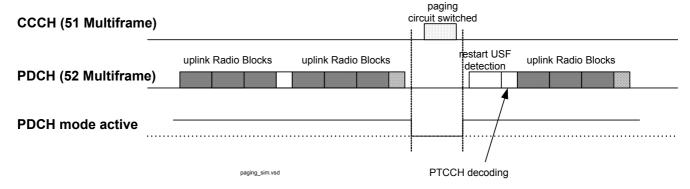

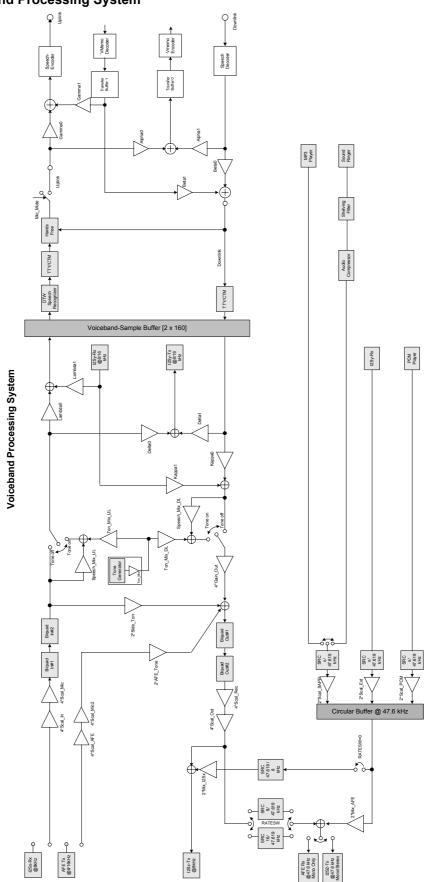

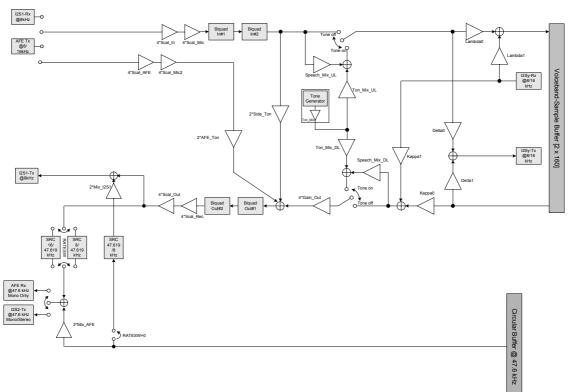

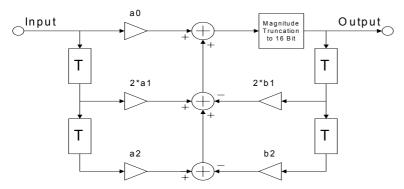

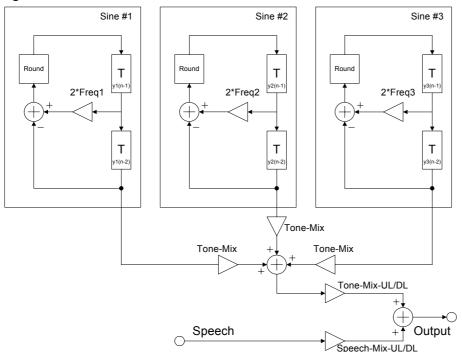

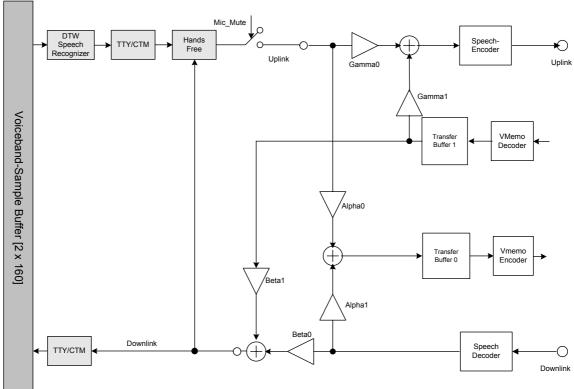

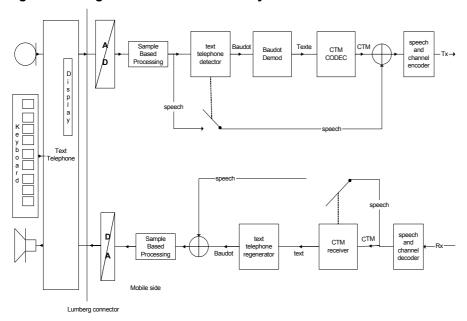

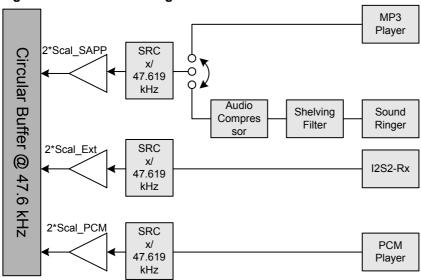

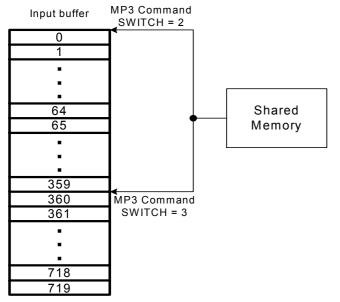

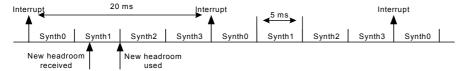

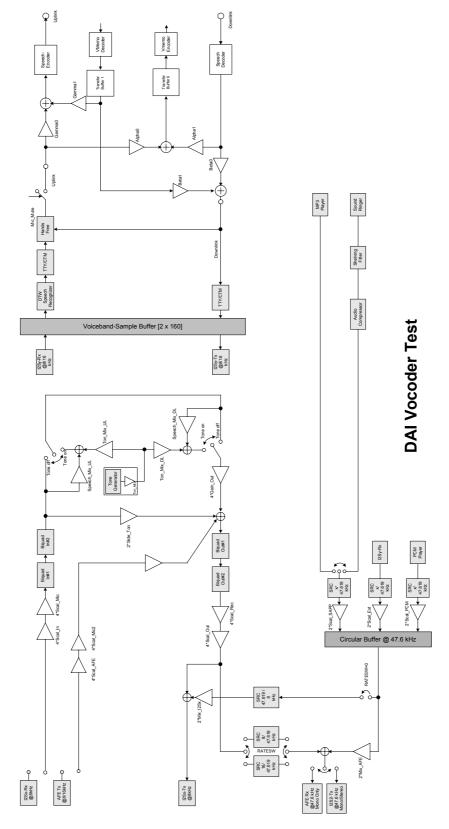

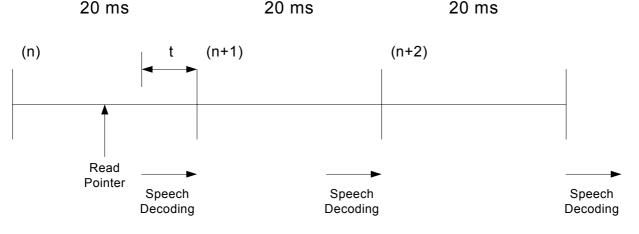

|                      | VTXCTRL        | Transmit Control register same as hardware register AFE_VTXCTRL, refer to [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |