# PMB6814 V1.0 E-POWERlite

Wireless Solutions

Never stop thinking.

Edition 2005-12-15

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2005.

All Rights Reserved.

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

### **Trademarks and Registered Terms**

$Bluemoon^{\$}, BlueNix^{\$}, M-GOLD^{\$}, SCT^{\$}, Sieget^{\$}, Smarti^{\$}, UCP^{\$}, WDTC^{\$} \ are \ registered \ trademarks \ of \ Infine on \ Technologies \ AG.$

S-GOLD™, E-GOLD™ are trademarks of Infineon Technologies AG.

## PMB6814 V1.0 E-POWERlite Table of Contents

## **CONFIDENTIAL**

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Introduction Revision History Overview Feature Overview Feature Comments Typical Application | 5<br>5<br>6 |

|--------------------------------------|----------------------------------------------------------------------------------------------|-------------|

| 2                                    | Pin Descriptions                                                                             |             |

| 2.1                                  | Pin Diagram                                                                                  |             |

| 2.2                                  | Pin Descriptions and Functions                                                               |             |

| 2.3                                  | Migration from SM-POWER V1.5 to E-POWERlite                                                  |             |

| 2.3.1                                | Drop-in Replacement                                                                          |             |

| 2.3.2                                | Migration of Pinning SM-POWER V0.5/V1.5/E-POWERlite                                          |             |

| 2.3.3                                | Migration of Registers                                                                       | 4           |

| 3                                    | Functional Description                                                                       | 6           |

| 3.1                                  | Overview of Power Supply Functions                                                           | 6           |

| 3.2                                  | Control Inputs and Standby Behaviour                                                         | 7           |

| 3.3                                  | Step-Down Converter for Baseband (SDBB)                                                      | 9           |

| 3.3.1                                | Automatic Switching between Modes 1                                                          | 9           |

| 3.4                                  | Regulator LANA                                                                               | 1           |

| 3.5                                  | Audio Amplifier                                                                              | 1           |

| 3.5.1                                | Power Dissipation                                                                            | 2           |

| 3.5.2                                | Click and Pop Protection                                                                     | 2           |

| 3.5.3                                | Tristate Outputs                                                                             |             |

| 3.5.4                                | Protection against Short Circuits 2                                                          | 5           |

| 3.5.5                                | Programmable Common Mode Voltage 2                                                           |             |

| 3.6                                  | Vibrator Driver 2                                                                            |             |

| 3.7                                  | LED Drivers                                                                                  |             |

| 3.7.1                                | Backlight LED Driver 2                                                                       |             |

| 3.7.2                                | Signalling LED Drivers                                                                       |             |

| 3.7.3                                | Precharge Signalling Function                                                                |             |

| 3.8                                  | Charge Control Function                                                                      |             |

| 3.8.1                                | Precharge Functionality                                                                      |             |

| 3.8.2                                | Constant Current Charging                                                                    |             |

| 3.8.3                                | Constant Voltage Charging                                                                    |             |

| 3.8.4                                | Pulse Charging 3                                                                             |             |

| 3.8.5                                | Charging Current Monitoring                                                                  |             |

| 3.9                                  | RTC Backup Battery Charging Function                                                         |             |

| 3.10                                 | Power On/Off and Reset Control Logic                                                         |             |

| 3.10.1                               | Insertion of Battery                                                                         |             |

| 3.10.2                               | Power-down Tristate Function of E-GOLDlite                                                   |             |

| 3.10.3                               | Turn-On                                                                                      |             |

| 3.10.4                               | Power-up Sequence                                                                            | 1           |

## PMB6814 V1.0 E-POWERlite Table of Contents

## CONFIDENTIAL

| 3.10.5             | Turn-off                                        | 38 |

|--------------------|-------------------------------------------------|----|

| 3.10.6             | Undervoltage Shutdown                           | 40 |

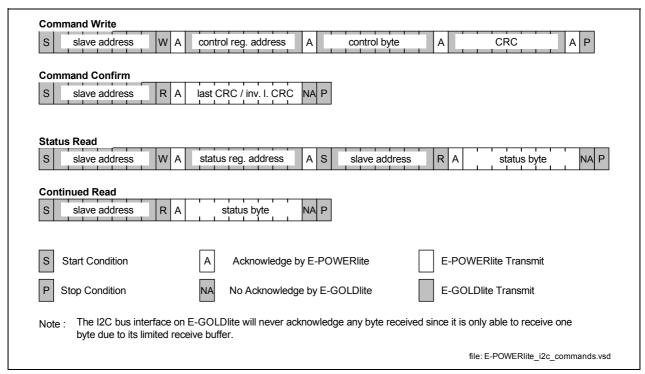

| 3.11               | I2C-Bus Interface                               | 41 |

| 3.11.1             | Device Address                                  | 41 |

| 3.11.2             | Command Write                                   | 41 |

| 3.11.3             | Command Confirmation                            | 42 |

| 3.11.4             | Status Read                                     | 42 |

| 3.11.5             | Continued Read                                  | 43 |

| 3.12               | Software-triggered System Reset                 | 43 |

| 3.13               | Error Flags, Debug Mode and Interrupts          | 43 |

| 3.13.1             | Error Flags                                     | 43 |

| 3.13.2             | Debug Mode                                      | 44 |

| 3.13.3             | Interrupts                                      | 44 |

| 3.14               | Overtemperature Warning                         | 44 |

| 3.15               | Overtemperature Shutdown                        | 45 |

| 4                  | Register Description                            | 46 |

| 4.1                | Control Registers                               |    |

| 4.2                | Status Registers                                |    |

| 5                  | Electrical Characteristics                      | 61 |

| <b>5</b><br>5.1    | Absolute Maximum Ratings                        |    |

| 5.1<br>5.2         | Operating Range                                 |    |

| 5.2<br>5.3         | Supply Currents                                 |    |

| 5.4                | AC/DC Characteristics of Common Functions       |    |

| 5. <del>5</del>    | AC/DC Characteristics of Digital Pins           |    |

| 5.6                | AC/DC Characteristics of Power Supply Functions |    |

| 5.7                | AC/DC Characteristics of Audio Amplifier        |    |

| 5. <i>1</i><br>5.8 | AC/DC Characteristics of Addio Ampliner         |    |

|                    |                                                 |    |

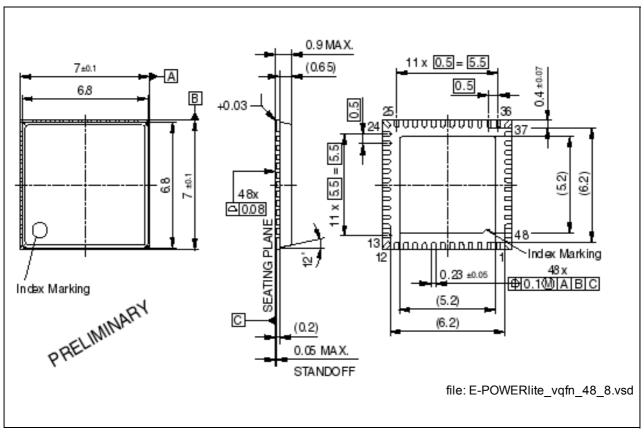

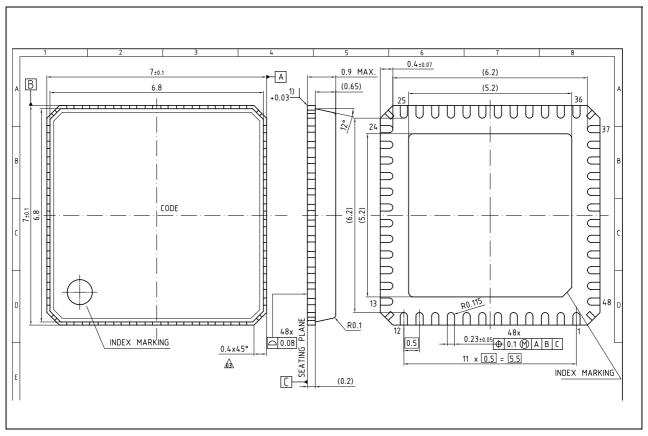

| 6                  | Package Information                             | 85 |

## 1 Introduction

## 1.1 Revision History

## **Table 1-1** Revision History

| Current version  | Data Sheet                      | Rev. 1.1, 2005-12-15                         |

|------------------|---------------------------------|----------------------------------------------|

| Previous version | Target Specification Data Sheet | Rev. 3.2, 2004-07-04<br>Rev. 1.0, 2005-10-19 |

## Table 1-2 Changes for Data Sheet Rev. 1.1

| Page/Chapter | Change                                  |

|--------------|-----------------------------------------|

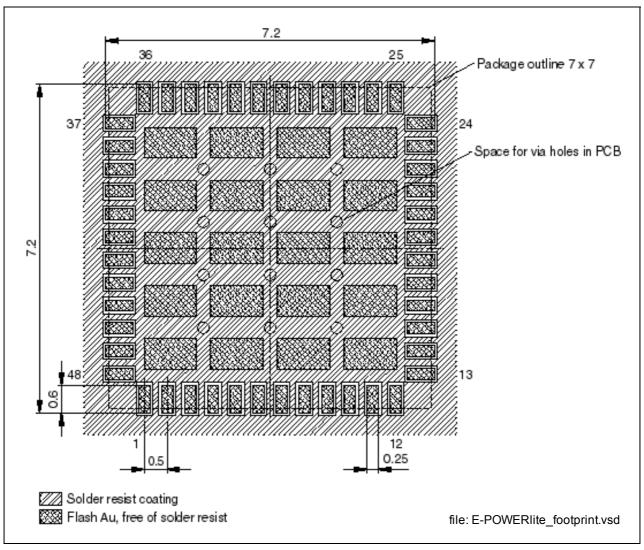

| Table 6-2    | Package drawing for PG-VQFN-48-15 added |

## 1.2 Overview

PMB6814 V1.0 E-POWERlite is a highly integrated power and battery management IC for mobile handsets. The device provides all power supply functions (except for the RF PA) by minimizing external device count. It is designed for usage with:

- E-GOLDlite baseband device

- SMARTi-SD RF device

#### 1.3 Feature Overview

- Highly efficient step-down converter for main digital baseband supply including core, DSP and memory interface (External Bus Unit).

- Support of E-GOLDlite standby power-down concept

- Low-drop-out (LDO) regulators for flash and mobile RAM memory devices

- LDO regulators for baseband I/O supply

- · LDO regulator for analog mixed-signal section of E-GOLDlite

- · Low-noise LDO regulators for RF devices

- · Audio amplifier for hands-free operation and ringing

- Charge control for charging of NiMH and Li-Ion/Polymer batteries under software control

- Pre-charge current generator with selectable current level

- · RTC regulator with ultra-low guiescent current

- · Backlight LEDs driver with current selection and PWM dimming function

- Two single LED driver outputs for signalling

- · Vibrator driver with adjustable voltage

- · Fully controllable by software via I2C-bus

Data Sheet 5 Rev. 1.1, 2005-12-15

- Temperature and battery voltage sensors

- Interrupt channels for peripherals

- · System debug mode

- PG-VQFN 48 package with heat sink and non-protruding leads

Note: Since appropriate security functions have been implemented in E-GOLDlite no ID register is available on E-POWERlite.

Note: Since a highly versatile watch-dog timer is implemented on E-GOLDlite no watch-dog timer is available on E-POWERlite.

#### 1.4 Feature Comments

PMB6814 V1.0 E-POWERlite is a further step on the successful E-Power product line with enhanced and optimized functionality.

E-POWERlite features a baseband supply concept with a DC/DC step-down converter (SDBB) cascaded by two linear regulators (LBB1, LBB2)

- E-POWERlite's DC/DC converter makes up to 40 % reduction of battery current possible.

- SDBB has high efficiency up to 95% and a power save mode.

- Memory interface is directly supported by the SDBB

- SDBB can also act as main supply voltage for the E-GOLDlite baseband device.

- Two linear regulators for DSP and core of E-GOLDlite are cascaded after the SDBB

E-POWERlite supports the standby power-down concept of E-GOLDlite by temporarily switching off the linear regulator LBB1 for the DSP during mobile standby. In this phase the C166 controller and most peripherals are kept powered-up with power being supplied by the other linear regulator LBB2.

E-POWERlite includes a fully differential audio amplifier

- Can drive loads down to 8 Ohm (nominal)

- Allows hands-free operation and polyphone ringing

- Programmable common mode voltage for maximum output power

- Adjustable gain

- Mute switch

- Click and pop protection

E-POWERlite also integrates a charging function for Li-Ion, Li-Polymer and NiMh batteries

- Precharge current source with two voltage levels

- Constant current / constant voltage charging with 3 different termination voltages

- Programmable charge current limitation for use with different batteries

- Freely programmable pulse charging to reduce the thermal power dissipation in the constant voltage charging phase

- Top-off charge current sensing

Data Sheet 6 Rev. 1.1, 2005-12-15

## E-POWERlite fully supports LED and vibra motor functionality

- No external components needed

- Driver for backlight LEDs adjustable in steps up to 140 mA and with soft turn on and off by PWM dimming

- Two driver outputs for single LEDs for precharge indication and signalling with i.e. change of colour

- Driver for Vibra Motor with adjustable voltages, soft startup / shutdown and current limitation

#### E-POWERlite offers several control functions

- Power-on reset generator with logic state machine

- I2C bus interface

- I2C bus configurable mode control logic with ON (push-button or RTC), VCXOEN

- Programmable interrupt channels to handle peripherals

- Monitoring of charging functions

- Undervoltage shut-down

- Errorflags (volatile or non-volatile) from many power-supply functions and thermal sensor in order to debug system

- Overtemperature shut-down

- Overtemperature warning

- Support of E-GOLDlite standby power-down concept

- Support of E-GOLDlite power-down pad tristate function

## E-POWERlite comes in a PG-VQFN 48 package

- Minimized board footprint of 7 x 7 mm

- Superior thermal characteristics with a thermal resistance of 20 K/W typical

- Power dissipation up to 2 W can be handled

## 1.5 Typical Application

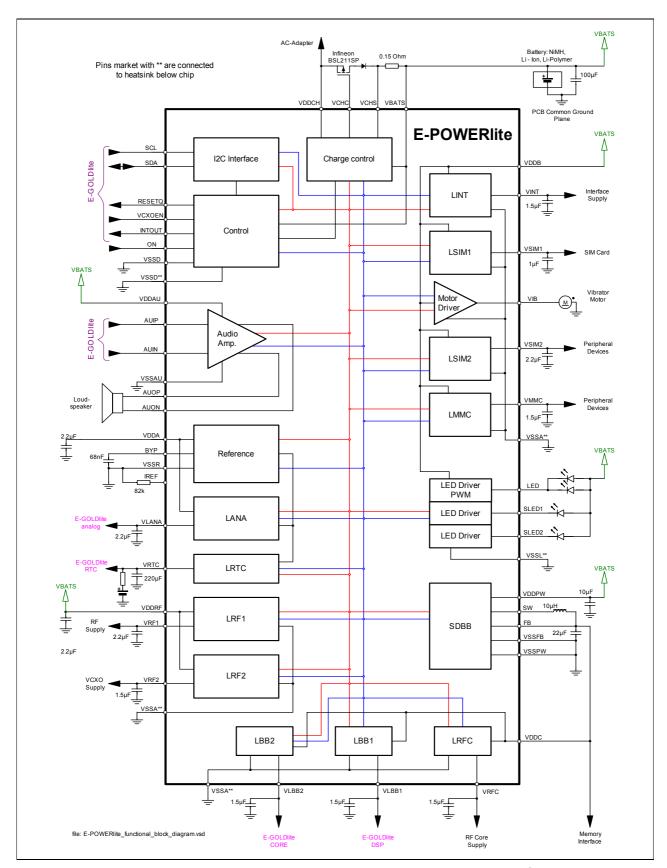

A functional block diagram with typical application circuitry is shown in **Figure 1-1**. Important application information:

- In general all peripheral passive devices as shown in Figure 1-1 must be attached to E-POWERlite to enable full function.

- If the charging function is not used pin VCHS has to be shorted to pin VBATS in any case.

Data Sheet 7 Rev. 1.1, 2005-12-15

Figure 1-1 Functional Block Diagram with Typical Application Circuitry

Data Sheet 8 Rev. 1.1, 2005-12-15

## 2 Pin Descriptions

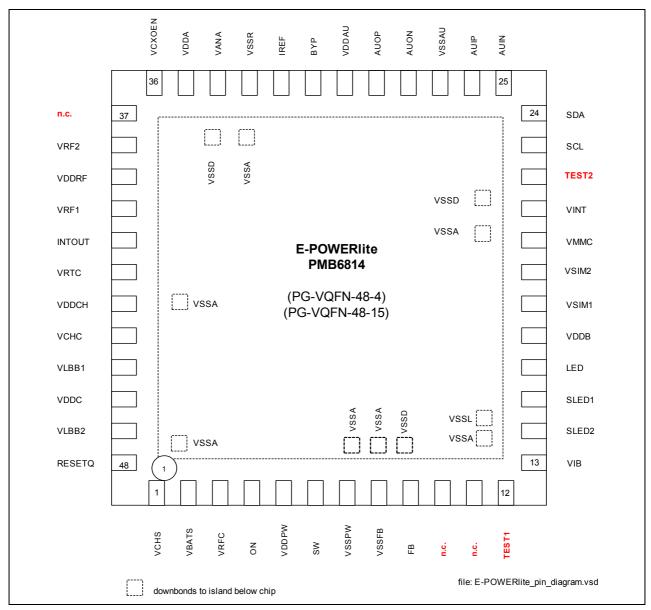

## 2.1 Pin Diagram

Figure 2-1 Pin Diagram of E-POWERlite (Top View)

Data Sheet 9 Rev. 1.1, 2005-12-15

## 2.2 Pin Descriptions and Functions

Table 2-1 PMB6814 V1.0 E-POWERlite Pin List

| Pos. | Symbol | Pin <sup>1)</sup><br>Type | Function                                                                                  |  |  |

|------|--------|---------------------------|-------------------------------------------------------------------------------------------|--|--|

| 1    | VCHS   | I/O                       | Charge current sense / precharge output                                                   |  |  |

| 2    | VBATS  | I                         | Battery voltage sense                                                                     |  |  |

| 3    | LRFC   | 0                         | Supply for RF core                                                                        |  |  |

| 4    | ON     | I                         | Push-button or RTC power on                                                               |  |  |

| 5    | VDDPW  | S                         | Input voltage for SDBB output stage                                                       |  |  |

| 6    | SW     | 0                         | SDBB output                                                                               |  |  |

| 7    | VSSPW  | S                         | Ground for SDBB output stage                                                              |  |  |

| 8    | VSSFB  | S                         | Ground sense of SDBB                                                                      |  |  |

| 9    | FB     | I                         | Feedback of SDBB                                                                          |  |  |

| 10   | -      | -                         | N.c.                                                                                      |  |  |

| 11   | -      | -                         | N.c.                                                                                      |  |  |

| 12   | TEST1  | I                         | Test pin, connect to VSS for normal operation                                             |  |  |

| 13   | VIB    | 0                         | Vibrator motor driver output                                                              |  |  |

| 14   | SLED2  | 0                         | Supply for second single LED                                                              |  |  |

| 15   | SLED1  | 0                         | Supply for first single LED                                                               |  |  |

| 16   | LED    | 0                         | Supply for backlight LED                                                                  |  |  |

| 17   | VDDB   | S                         | Input voltage for peripheral regulators                                                   |  |  |

| 18   | VSIM1  | 0                         | Supply for SIM Card and E-GOLDlite SIM interface                                          |  |  |

| 19   | VSIM2  | 0                         | Supply for peripheral devices                                                             |  |  |

| 20   | VMMC   | 0                         | Supply for peripheral devices                                                             |  |  |

| 21   | VINT   | 0                         | Supply for E-GOLDlite interfaces (I2C, SSC, Keypad)                                       |  |  |

| 22   | TEST2  | S                         | Test pin, connect to VSS for normal operation                                             |  |  |

| 23   | SCL    | I                         | I2C Bus clock                                                                             |  |  |

| 24   | SDA    | I/O                       | I2C Bus data / acknowledge                                                                |  |  |

| 25   | AUIN   | l                         | Differential audio amplifier input n from E-GOLDlite acts also as digital ringing input n |  |  |

| 26   | AUIP   | l                         | Differential audio amplifier input p from E-GOLDlite acts also as digital ringing input p |  |  |

Table 2-1 PMB6814 V1.0 E-POWERlite Pin List

| Pos. | Symbol | Pin <sup>1)</sup><br>Type | Function                                                        |  |  |

|------|--------|---------------------------|-----------------------------------------------------------------|--|--|

| 27   | VSSAU  | S                         | Ground for audio amplifier                                      |  |  |

| 28   | AUON   | 0                         | Differential audio amplifier output n                           |  |  |

| 29   | AUOP   | 0                         | Differential audio amplifier output p                           |  |  |

| 30   | VDDAU  | S                         | Input voltage for audio amplifier                               |  |  |

| 31   | BYP    | 0                         | Bypass capacitor for bandgap reference                          |  |  |

| 32   | IREF   | 0                         | Current reference resistor                                      |  |  |

| 33   | VSSR   | S                         | Ground for references                                           |  |  |

| 34   | VANA   | 0                         | Supply for analog macro of E-GOLDlite                           |  |  |

| 35   | VDDA   | S                         | Input voltage for analog regulators                             |  |  |

| 36   | VCXOEN | I                         | Mode toggling by E-GOLDlite                                     |  |  |

| 37   | -      | -                         | N.c.                                                            |  |  |

| 38   | VRF2   | 0                         | Supply for External Oscillator                                  |  |  |

| 39   | VDDRF  | S                         | Input voltage for RF regulators                                 |  |  |

| 40   | VRF1   | 0                         | Supply for RF IC                                                |  |  |

| 41   | INTOUT | 0                         | Interrupt output to E-GOLDlite                                  |  |  |

| 42   | VRTC   | 0                         | Supply for E-GOLDlite real time clock domain                    |  |  |

| 43   | VDDCH  | S                         | Input voltage for charge control (from external AC-adapter)     |  |  |

| 44   | VCHC   | 0                         | Control output for external PMOS device                         |  |  |

| 45   | VLBB1  | 0                         | Supply for E-GOLDlite DSP                                       |  |  |

| 46   | VDDC   | S                         | Input voltage for baseband regulators and vibrator motor driver |  |  |

| 47   | VLBB2  | 0                         | Supply for E-GOLDlite core including C166                       |  |  |

| 48   | RESETQ | 0                         | Resetq output to E-GOLDlite                                     |  |  |

| *    | VSSA   | S                         | 5 grounds for analog circuits                                   |  |  |

| *    | VSSD   | S                         | 3 grounds for digital circuits                                  |  |  |

| *    | VSSL   | S                         | Ground for LED drivers                                          |  |  |

$<sup>^{1)}\;\;</sup>$  I : Input, O : Output, S : Supply, \*: connected to island below chip

## 2.3 Migration from SM-POWER V1.5 to E-POWERlite

## 2.3.1 Drop-in Replacement

**Table 2-2** shows the change of pinning and application for SM-POWER V1.5 and E-POWERlite. The following issues must be obeyed for a design that supports both devices (drop-in replacement):

- LRF3EN must be connected to GND

- For stability reasons the application cirucit as proposed in the SM-POWER V1.5 data sheet should be applied to VUPU, VRF3, VUSB and VBUS.

Table 2-2 Changes in Pinout and Application

| Pos. | SM-POWER<br>V1.5 | E      | -POWERlite                                                                   | Common Application for SM-POWER V1.5 and                                                                             |

|------|------------------|--------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|      | Symbol           | Symbol | Remark                                                                       | E-POWERlite                                                                                                          |

| 10   | VUPU             | n.c.   | Pin internally not connected.                                                | Can be left unconnected for E-POWERlite.                                                                             |

| 37   | VRF3             | n.c.   | Pin internally not connected.                                                | For drop-in replacement: Application as proposed for SM-POWER V1.5.                                                  |

| 11   | VUSB             | n.c.   | Pin internally not connected.                                                | When using E-POWERlite external components can be omitted.                                                           |

| 12   | VBUS             | TEST1  | Pin internally pulled to VSS. Pin only used for test purposes. <sup>1)</sup> | Three possibilities: 1 Connect pin to VSS. 2 Leave pin unconnected. 3 Use application as proposed for SM-POWER V1.5. |

| 22   | LRF3EN           | TEST2  | Pin only used for test purposes. <sup>2)</sup>                               | Connect pin to VSS.                                                                                                  |

<sup>1)</sup> Used for scan path testing.

## 2.3.2 Migration of Pinning SM-POWER V0.5/V1.5/E-POWERlite

**Table 2-3** compares the pinning of the different POWER versions.

Data Sheet 12 Rev. 1.1, 2005-12-15

<sup>2)</sup> Used for scan path testing.

Table 2-3 Pin List Comparison between POWER Chips

| Pos. | SM POWER | SM-POWER | E-POWER lite | Remark                           |

|------|----------|----------|--------------|----------------------------------|

|      | V0.5     | V1.5     | _            |                                  |

| 1    | VCHS     | VCHS     | VCHS         |                                  |

| 2    | VBATS    | VBATS    | VBATS        |                                  |

| 3    | ON       | LRFC     | LRFC         | Difference between V0.5 and V1.5 |

| 4    | VIB      | ON       | ON           | Difference between V0.5 and V1.5 |

| 5    | VDDPW    | VDDPW    | VDDPW        |                                  |

| 6    | SW       | SW       | SW           |                                  |

| 7    | VSSPW    | VSSPW    | VSSPW        |                                  |

| 8    | VSSFB    | VSSFB    | VSSFB        |                                  |

| 9    | FB       | FB       | FB           |                                  |

| 10   | VUPU     | VUPU     |              | E-POWERlite modified             |

| 11   | VUSB     | VUSB     |              | E-POWERlite modified             |

| 12   | VBUS     | VBUS     | TEST1        | E-POWERlite modified             |

| 13   | VCXOEN   | VIB      | VIB          | Difference between V0.5 and V1.5 |

| 14   | SLED2    | SLED2    | SLED2        |                                  |

| 15   | SLED1    | SLED1    | SLED1        |                                  |

| 16   | LED      | LED      | LED          |                                  |

| 17   | VDDB     | VDDB     | VDDB         |                                  |

| 18   | VSIM1    | VSIM1    | VSIM1        |                                  |

| 19   | VSIM2    | VSIM2    | VSIM2        |                                  |

| 20   | VMMC     | VMMC     | VMMC         |                                  |

| 21   | VINT     | VINT     | VINT         |                                  |

| 22   | LRF3EN   | LRF3EN   | TEST2        | E-POWERlite modified             |

| 23   | SCL      | SCL      | SCL          |                                  |

| 24   | SDA      | SDA      | SDA          |                                  |

| 25   | AUIN     | AUIN     | AUIN         |                                  |

| 26   | AUIP     | AUIP     | AUIP         |                                  |

| 27   | VSSAU    | VSSAU    | VSSAU        |                                  |

| 28   | AUON     | AUON     | AUON         |                                  |

| 29   | AUOP     | AUOP     | AUOP         |                                  |

Table 2-3 Pin List Comparison between POWER Chips

| Pos.  | SM POWER | SM-POWER | E-POWER lite  | Remark                           |

|-------|----------|----------|---------------|----------------------------------|

| 1 03. | V0.5     | V1.5     | L-1 OWEN IIIC | Kemark                           |

| 30    | VDDAU    | VDDAU    | VDDAU         |                                  |

| 31    | BYP      | BYP      | BYP           |                                  |

| 32    | IREF     | IREF     | IREF          |                                  |

| 33    | VSSR     | VSSR     | VSSR          |                                  |

| 34    | VANA     | VANA     | VANA          |                                  |

| 35    | VDDA     | VDDA     | VDDA          |                                  |

| 36    | VRF0     | VCXOEN   | VCXOEN        | Difference between V0.5 and V1.5 |

| 37    | VRF3     | VRF3     |               | E-POWERlite modified             |

| 38    | VRF2     | VRF2     | VRF2          |                                  |

| 39    | VDDRF    | VDDRF    | VDDRF         |                                  |

| 40    | VRF1     | VRF1     | VRF1          |                                  |

| 41    | INTOUT   | INTOUT   | INTOUT        |                                  |

| 42    | VRTC     | VRTC     | VRTC          |                                  |

| 43    | VDDCH    | VDDCH    | VDDCH         |                                  |

| 44    | VCHC     | VCHC     | VCHC          |                                  |

| 45    | VLBB1    | VLBB1    | VLBB1         |                                  |

| 46    | VDDC     | VDDC     | VDDC          |                                  |

| 47    | VLBB2    | VLBB2    | VLBB2         |                                  |

| 48    | RESETQ   | RESETQ   | RESETQ        |                                  |

| *     | VSSA     | VSSA     | VSSA          |                                  |

| *     | VSSD     | VSSD     | VSSD          |                                  |

| *     | VSSCHP   | VSSCHP   |               |                                  |

| *     |          | VSSUSB   |               | Difference between V0.5 and V1.5 |

| *     | VSSL     | VSSL     | VSSL          |                                  |

## 2.3.3 Migration of Registers

**Table 2-4** compares the register contents of the SM-POWER V1.5 and E-POWERlite. The register access is completely identical for the SM-POWER V1.5 and E-POWERlite with the following exceptions:

• The registers of circuits that have been removed in the E-POWERlite have no function.

Data Sheet 14 Rev. 1.1, 2005-12-15

- The function of LRF3EN does not exist.

- For using the enhanced features of the audio amplifier register AUDCTRL2 must be accessed.

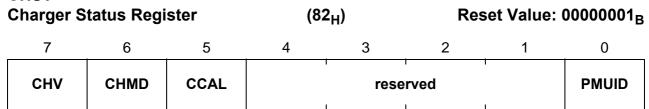

- It is possible to distinguish by software between E-POWERlite and SM-POWER V1.5 by reading bit 0 of register **CHST**.

Table 2-4 Register Comparison between POWER Chips

| Address [Hex]. | Access | SM-POWER V1.5 | E-POWERlite | Function inside<br>E-POWERlite |

|----------------|--------|---------------|-------------|--------------------------------|

| 00             | W      | -             | -           |                                |

| 01             | W      | RESCTRL       | RESCTRL     | Reset control                  |

| 02             | W      | PWCTRL1       | PWCTRL1     | LINT, LANA, LBB1, LBB2         |

| 03             | W      | PWCTRL2       | PWCTRL2     | SDBB                           |

| 04             | W      | CHCTRL1       | CHCTRL1     | Charger control                |

| 05             | W      | INTCTRL1      | INTCTRL1    | Interrupt control              |

| 06             | W      | INTCTRL2      | INTCTRL2    | Interrupt control              |

| 07             | W      | PWCTRL3       | PWCTRL3     | LRF2                           |

| 08             | W      | CHCTRL2       | CHCTRL2     | Charger control                |

| 0A             | W      | LEDCTRL1      | LEDCTRL1    | LED control                    |

| 0B             | W      | DRVCTRL       | DRVCTRL     | Vibrator driver control        |

| 0C             | W      | USBCTRL       | AUDCTRL2    | Audio amplifier control        |

| 0D             | W      | AUDCTRL       | AUDCTRL     | Audio amplifier control        |

| 0E             | W      | PWCTRL4       | PWCTRL4     | LRFC, LRF1                     |

| 11             | W      | PWCRTL5       | PWCRTL5     | LSIM, LSIM2                    |

| 12             | W      | PWCTRL6       | PWCTRL6     | LMMC                           |

| 13             | W      | LEDCTRL2      | LEDCTRL2    | LED control                    |

| 80             | R      | GEF1          | GEF1        | General error flags            |

| 81             | R      | ISF           | ISF         | Interrupt source flags         |

| 82             | R      | CHST          | CHST        | Charger status                 |

| 83             | R      | GEF2          | GEF2        | General error flags            |

Data Sheet 15 Rev. 1.1, 2005-12-15

## **3** Functional Description

## 3.1 Overview of Power Supply Functions

An overview of the power supply functions is given in **Table 3-1**. Output voltage values after start-up are printed bold.

Table 3-1 Overview of Power Supplies

| Regulator |                                  | Output<br>Voltage                   | Min.<br>Output<br>Current | Auto<br>Startup | Supplied Device / Remark                                            |

|-----------|----------------------------------|-------------------------------------|---------------------------|-----------------|---------------------------------------------------------------------|

| Name      | Type                             | ٧                                   | mA                        |                 |                                                                     |

| SDBB      | DC/DC<br>converter               | 1.92<br>1.86<br><b>1.80</b><br>1.50 | 400                       | Yes             | Input for LBB1, LBB2 and LRFC, supply for EBU, SDRAM I/O and others |

| LBB1      | linear<br>regulator              | <b>1.50</b><br>1.65                 | 170                       | Yes             | E-GOLDlite DSP (TeakLite®) supply (supplied by SDBB)                |

| LBB2      | linear<br>regulator              | <b>1.50</b><br>1.65                 | 170                       | Yes             | E-GOLDlite core supply including C166 (supplied by SDBB)            |

| LANA      | low-noise<br>LDO                 | 2.65                                | 220                       | Yes             | Supply for analog part in E-GOLDlite                                |

| LINT      | LDO                              | 2.72                                | 135                       | Yes             | E-GOLDlite interface supply: I2C, SSC1-3, ETM                       |

| LSIM      | LDO                              | <b>2.85</b> 1.80                    | 22                        | Yes             | E-GOLDlite SIM Interface                                            |

| LSIM2     | LDO                              | <b>2.85</b> 1.80                    | 200                       | Yes             | Supply for peripherals                                              |

| LMMC      | LDO                              | <b>2.85</b> 1.80                    | 22                        | Yes             | Supply for peripherals                                              |

| LRFC      | low-noise<br>linear<br>regulator | 1.50                                | 120                       | No              | SMARTi-SD core<br>(supplied by SDBB)                                |

| LRF1      | low-noise<br>LDO                 | 2.50                                | 120                       | No              | SMARTi-SD main supply                                               |

Data Sheet 16 Rev. 1.1, 2005-12-15

Table 3-1 Overview of Power Supplies

| Regulator |                     | Output<br>Voltage   | Min.<br>Output<br>Current | Auto<br>Startup | Supplied Device / Remark    |

|-----------|---------------------|---------------------|---------------------------|-----------------|-----------------------------|

| Name      | Туре                | V                   | mA                        |                 |                             |

| LRF2      | low-noise<br>LDO    | 2.70<br><b>2.50</b> | 10                        | Yes             | Supply for VCXO             |

| LRTC      | linear<br>regulator | 2.11                | 0.3                       | Yes             | Ultra-low zero-load current |

## 3.2 Control Inputs and Standby Behaviour

## **Control Input ON**

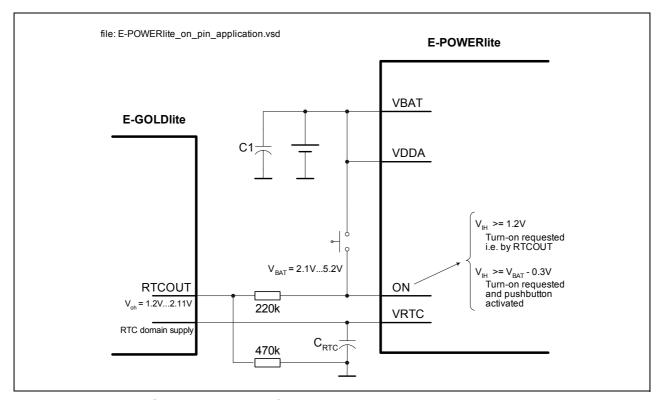

ON is a power-on input for E-POWERlite with 2 active high levels (see **Figure 3-1**). It can be triggered by

- · a push button

- the RTCOUT output of the E-GOLDlite

To detect if the push-button is pressed during system operation the logic level at pin ON or a level change (if bit EION in INTCTRL2 is set to 1) is recorded in bit LON of the ISF register. LON is only set if the high level of the voltage at pin ON is above V<sub>IHdet</sub> (see Table 5-8 "AC/DC Characteristics of Digital Signals" on Page 64).

Data Sheet 17 Rev. 1.1, 2005-12-15

Figure 3-1 Pin ON Application Circuit

## **Control Input VCXOEN**

VCXOEN is a control signals that allows switching the state of the power mangement functions of the PMB6814 V1.0 E-POWERlite with a single signal.

VCXOEN = 0, standby mode

VCXOEN = 1, active mode

- The regulators LBB1, LRFC, LRF1, LRF2 can be programmed to a configuration that allows to control the **on/off** state with VCXOEN.

- The regulators LINT, LSIM, LSIM2, LMMC can be programmed to a configuration that allows to control the **on/standby** state with VCXOEN.

- The SDBB regulator can be programmed to a configuration that allows to control the toggling between PWM- and power saving PFM-mode with VCXOEN.

**Table 3-2**shows a list of all functions that can be controlled by VCXOEN and the required register programming to allow control with VCXOEN.

Table 3-2 Control Function of VCXOEN

| Regulator | Register Setting to allow | Function of Regulator |            |  |

|-----------|---------------------------|-----------------------|------------|--|

|           | Control by VCXOEN         | VCXOEN = 0            | VCXOEN = 1 |  |

| LRFC      | PWCTRL4 / LRFCMD = 01     | off                   | on         |  |

Data Sheet 18 Rev. 1.1, 2005-12-15

Table 3-2 Control Function of VCXOEN

| Regulator | Register Setting to allow                          | Function of Regulator |            |  |

|-----------|----------------------------------------------------|-----------------------|------------|--|

|           | Control by VCXOEN                                  | VCXOEN = 0            | VCXOEN = 1 |  |

| LRF1      | PWCTRL4 / LRF1MD = 01                              | off                   | on         |  |

| LRF2      | PWCTRL3 / LRF2MD = 01<br>PWCTRL3 / LRF2MD = 10     | off                   | on         |  |

| LBB1      | PWCTRL1 / LBBMD = 01                               | off                   | on         |  |

| SDBB      | PWCTRL2 / SDBBMD = 01                              | PFM                   | PWM        |  |

| LINT      | PWCTRL1 / LINTMD = 0                               | standby               | on         |  |

| LSIM      | PWCTRL5 / LSIMMD = 01                              | standby               | on         |  |

| LSIM2     | PWCTRL5 / LSIM2MD = 001<br>PWCTRL5 / LSIM2MD = 011 | standby               | on         |  |

| LMMC      | PWCTRL6 / LMMCMD = 01                              | standby               | on         |  |

In standby mode the dynamic performance of regulators LINT, LSIM, LSIM2 and LMMC is reduced. Please see **Table 5-12**, **Table 5-13** and **Table 5-14** for details.

## 3.3 Step-Down Converter for Baseband (SDBB)

The Step-Down Converter SDBB (Step-Down Baseband) converts the battery voltage to an artificial supply rail VDDC between 1.50 V and 1.92 V (programmable). VDDC provides the input current for:

- Baseband regulators LBB1 and LBB2

- External bus unit of E-GOLDlite

- I/O of an external memory IC

- LRFC regulator

Any current demand from these consumers counts against the specified output current and output current change rate of SDBB.

The SDBB can be operated in two different modes:

- PWM: for high currents

- PFM: for low currents (minimized power consumption!)

## 3.3.1 Automatic Switching between Modes

The PMB6814 V1.0 E-POWERlite can react automatically to increased current requirements by switching automatically from PFM mode to PWM mode.

If an overload condition occurs in PFM mode and bit ASPWM in register **PWCTRL2** is set an automatic switch-back to PWM mode will occur.

Data Sheet 19 Rev. 1.1, 2005-12-15

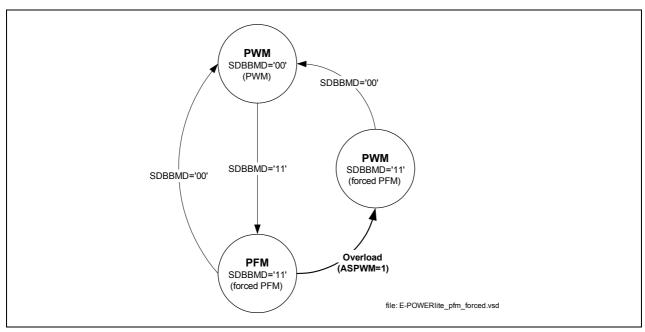

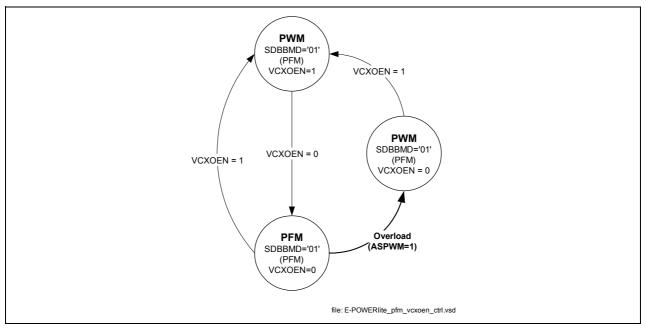

To re-enable PFM mode after an automatic switch-back, first PWM mode must be enabled again by hardware. PFM mode can be enabled either by software control or by using VCXOEN as control signal. The state diagram for switching back to PFM is shown in **Figure 3-2** and **Figure 3-3** for both modes.

- **Software controlled mode:** In case of forced PFM mode the register must be reset to PWM mode before it can be programmed to forced PFM mode again. **Figure 3-2** shows the state diagram.

- VCXOEN controlled mode: In case of VCXOEN controlled PFM mode the next falling edge of signal VCXOEN will re-enable PFM mode. Figure 3-3 shows the state diagram.

Figure 3-2 State Diagram for Switch-back from Software controlled PFM Mode

Data Sheet 20 Rev. 1.1, 2005-12-15

Figure 3-3 State Diagram for Switch-back from VCXOEN controlled PFM Mode

## 3.4 Regulator LANA

Regulator LANA is designed to supply the analog part of the E-GOLDlite. The maximum supply current permits a maximum audio output power of 2 x 20 mW on the stereo headset outputs at a load of 15 Ohms.

## 3.5 Audio Amplifier

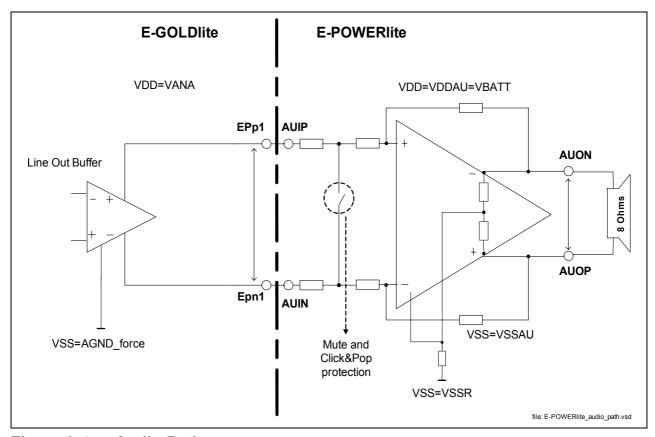

The audio buffer is a fully differential unity gain amplifier for amplification of the output signal on the E-GOLDlite outputs EPp1 and EPn1. The audio amplifier is directly supplied by the battery thereby permitting maximum output power and saving silicon for the regulator. This requires a high PSRR to be able to tolerate the high ripple voltage on the battery supply during transmit bursts generated by the PA.

The audio path interface between E-GOLDlite and E-POWERlite and its typical levels are shown in **Figure 3-4**. For good performance a PCB design with a low ohmic connection between the two grounds AGND force and VSSR is recommended.

Data Sheet 21 Rev. 1.1, 2005-12-15

Figure 3-4 Audio Path

The startup gain of the audio amplifier is -6.0 dB. It can be switched to -1.2 dB for digital ringing, +2.7 dB (permitting an audio output power of 400 mW on an 8 Ohm load) for voice and +7.6 dB for sound ringing.

## 3.5.1 Power Dissipation

Care has to be taken to limit the power dissipation of the audio amplifier in accordance with the thermal dissipation of other regulators, the thermal resistance of the package and the application environment.

The temperature of the junction of the device is sensed by a temperature sense element. If a temperatur of 120 °C is exceeded the overtemperatur warning sensor is triggered. Depending on activation of bit RAGOTW in register **INTCTRL2** the gain of the audio amplifier is reduced to -6.0 dB to reduce power dissipation.

## 3.5.2 Click and Pop Protection

Depop circuitry to prevent noise during turn-on and turn-off transitions is included in E-POWERlite's Audio Amplifier. The general principle of a click & pop circuit is to avoid unsymmetrical input signals during startup and shutdown of the amplifier circuit. In this

Data Sheet 22 Rev. 1.1, 2005-12-15

phase the audio amplifier can easily go into saturation by an unsymmetrical input. This may cause a disturbing click or pop noise.

The concept used in E-POWERlite is to raise the gain in 32µs steps:

- Starting point: amplifier is powered down and outputs are pulled to ground

- The first gain setting is "mute" which shorts the input signals across a part of the

amplifiere's input resistors. This prevents that an unsymmetrical signal is applied

during startup of the amplifier circuit. Note that an unsymmetrical signal can also be

the consequence of a DC offset in the audio path just before E-POWERlite.

- After 32 µs the next gain setting is activated, which is -6 dB. Then the next gain setting

is activated until the desired gain programmed in register AUDCTRL is reached.

In case the target gain is 7.6 dB the startup sequence may last for approximately 4 x 32  $\mu s$  = 128  $\mu s$ .

Shutdown via Bit AUDON in register **AUDCTRL** is done by the following sequence:

- Activate mute function for 32 μs.

- Decreasing the gain settings in 32 μs steps.

- Activate the pull-downs of the outputs.

Shutdown can take up to approximately 128 µs depending on the initial gain.

To avoid switching noise it is recommended to apply the following turn-on and turn-off sequences for the audio path:

- Turn on audio output of E-GOLDlite prior to audio amplifier on E-POWERlite.

- Turn off audio amplifier on E-POWERlite prior to audio output of E-GOLDlite.

## 3.5.3 Tristate Outputs

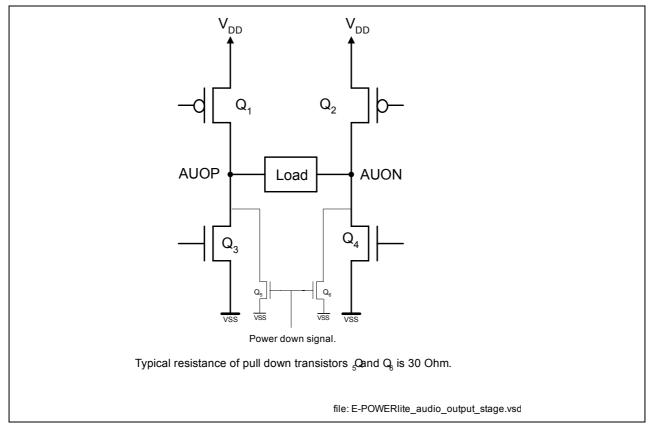

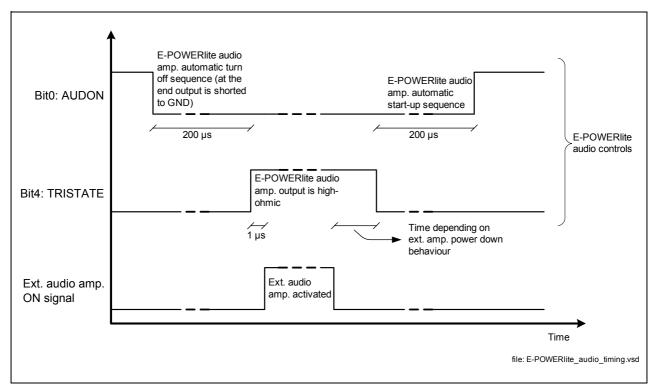

The E-POWERlite audio amplifier outputs can be programmed to tristate mode. This allows the system to connect another audio source to the loudspeaker in parallel for alternative usage. This feature can be activated by bit TRISTATE in register **AUDCTRL**. This bit is set to 0 by default enabling output's connection to ground for muting purposes, as shown in **Figure 3-5**. Switching this bit to 1 enables tri-state output. **Figure 3-6** shows a typical timing for entering and leaving tristate mode.

Data Sheet 23 Rev. 1.1, 2005-12-15

Figure 3-5 Audio Amplifier Output Stage

Note: It is recommended to set bit TRISTATE = 0 before starting the audio amplifier in E-POWERlite in order to have a well-defined startup point (for further details see **Figure 3-6**).

Data Sheet 24 Rev. 1.1, 2005-12-15

Figure 3-6 Combination of E-POWERlite internal Audio Amplifier and optional external Device: Turn-off, Tristate and Turn-on Timing Diagram

## 3.5.4 Protection against Short Circuits

The Audio Amplifier offers a short circuit protection by limiting the current to approx. 700mA if a short occurs between pins AUOP and AUON or AUOP/AUON and PCB ground.

Note: A short between AUOP/AUON and battery plus pole is not protected.

## 3.5.5 Programmable Common Mode Voltage

Per default the audio amplifier is designed for optimum performance concerning THD and power at a battery voltage of 3.3 V. To allow more output power for higher battery voltages the following programming is possible:

- The output common mode voltage of the audio amplifier can be programmed, depending on the battery voltage in register AUDCTRL2. It is recommendet to select the common mode voltage V<sub>outcm</sub> always to half the battery voltage V<sub>bat</sub>. This setup offers maximum possible output swing with lowest distortion. In this case the maximum possible output power is only limited by the battery voltage itself. In other words: Maximum possible output power depends on actual battery voltage (see Table 5-19).

- The gain of the audio amplifier can be programmed to maximum output swing even at limited input swing in register AUDCTRL2 and AUDCTRL.

Data Sheet 25 Rev. 1.1, 2005-12-15

#### 3.6 Vibrator Driver

The universal voltage source is a voltage-step programmable, switchable high side constant voltage source. The driver provides average load current limiting (see register **DRVCTRL** and **Table 5-23**). The low side of the load can be connected directly to ground.

The circuit has a built-in soft startup and shutdown function and does not need any external circuitry. If needed, a bypass filtering capacitor at the output can be added.

A short-circuit current limitation is included.

### 3.7 LED Drivers

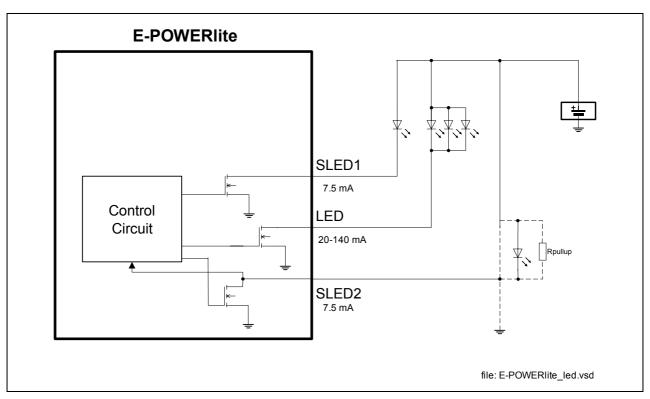

The complete configuration of the E-POWERlite LED drivers is shown in Figure 3-7.

Figure 3-7 Backlight and signalling LEDs

## 3.7.1 Backlight LED Driver

The backlight LED driver is suitable for driving most commercially available LEDs in the red, orange, yellow and green range. The driver is a switchable low side constant current source. It is programmable in 7 steps in the range from 20 mA to 140 mA with a step width of 20 mA (see register **LEDCTRL1**). The anode of the LEDs can be attached directly to the battery.

Data Sheet 26 Rev. 1.1, 2005-12-15

The power dissipation of the driver has to be taken into account for calculation of the maximum junction temperature. It can be minimized by selecting appropriate resistors in series with the LEDs.

The LED driver function consists of a PWM control with a fundamental frequency of about 60 Hz generated from the internal clock frequency of 500 kHz by division by 8192. Using register **LEDCTRL1** the duty cycle of the LED current can be set in 63 steps in the range from 0.5% to 100%. By sending a sequence of appropriate commands to E-POWERlite a soft dim function can easily be implemented.

## 3.7.2 Signalling LED Drivers

The signalling LED drivers are switchable low side constant current sources. In normal operation they can be controlled by the bits SLED1ON and SLED2On in register **LEDCTRL2**.

## 3.7.3 Precharge Signalling Function

During precharge phase the open drain LED driver at pin SLED1 is always enabled, thereby signalling precharging operation to the user if a LED is connected between this pin and the battery. If no additional LED is planned, SLED1 can be shorted to GND. During precharge phase the level on SLED2 sets the value of the precharge current of 60 mA or 120 mA depending on battery voltage (for details see Section 3.8.1).

## 3.8 Charge Control Function

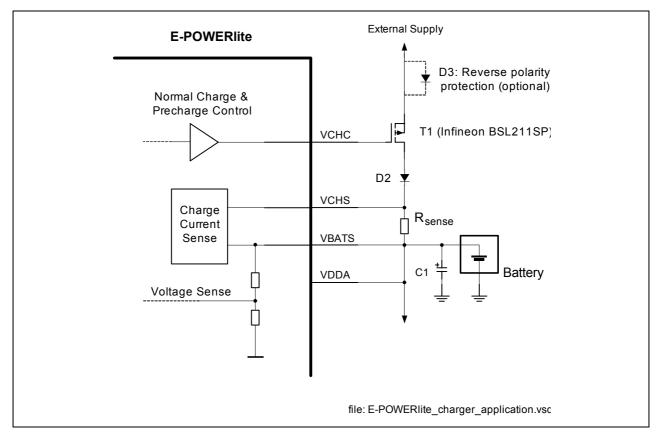

E-POWERlite provides together with external p-channel FETs like Infineon BSL 211SP, Siliconix Si3443 or Si3441 and an external AC-adapter a complete charge control function. The following batteries with 4.1, 4.2 or 5.2 V can be used:

- Li-lon (1 cell)

- Li-Ion-Polymer (1 cell)

- NiMH (3 cells), E-POWERlite devices to support NiMH cells are available on request

The supported external pass devices permit charging of the battery with currents of up to  $I_{ACadapt}$ . The voltage between pins VDDCH and VCHC is internally limited to less than 5.5 V. Thereby external FETs with a  $V_{GSmax}$  of 5.5 V can be used, even if the external AC adapter voltage rises up to 12 V.

The application circuit for charge control is shown in Figure 3-8.

Data Sheet 27 Rev. 1.1, 2005-12-15

Figure 3-8 Application Circuit for Charge Control

Diode D2 is required to prevent the drain-bulk diode of FET T1 from discharging the battery when the AC adapter voltage drops below the battery voltage.

Diode D3 is optional if reverse polarity protection is required because plugs are mistakeable.

Note: In case VDDCHmin of 5 V is required please avoid diode D3 by using a mechanical reverse polarity protection because it will further reduce the headroom voltage which is available for charging.

The following charge modes are supported by E-POWERlite:

When the AC-adapter is plugged:

Precharge function for deeply discharged batteries

When the AC adapter is plugged and battery voltage has exceeded V<sub>BATon</sub>.

- Constant current charging with programmable current limitation from 400 mA to 1.1 A.

- Constant voltage charging with 3 programmable voltage limitations for Li-lon, Li-Polymer and NiMH batteries

- Pulse charging option with selectable pulse width for top-off charging of Li-lon batteries

- Charging current monitoring for handling the top-off charging phase of Li-lon batteries.

Data Sheet 28 Rev. 1.1, 2005-12-15

## 3.8.1 Precharge Functionality

The precharge current function delivers a typical current of  $I_{Prech}$  (see **Table 5-24**) to the battery whenever the AC adapter is plugged. This current is used for bringing up a deeply discharged battery to a voltage level where the system can turn on again. This high amount of precharge current is necessary to ensure sufficient supply during the system startup phase when the controller usually boots its software. A proper startup is therefore possible even with deeply discharged batteries.

A selection between two precharge current values of  $I_{Prech1}$  and  $I_{Prech2}$  is possible by the logic level at pin SLED2. With deeply discharged batteries (voltages of about 1.2 V or less) only the precharge current of  $I_{Prech1}$  is allowed (see **Table**). The precharge current can be set as shown in **Figure 3-7**: if both  $I_{Prech1}$  precharge current and a signalling LED are needed. A pull-up resistor should then be put in parallel to the LED connected to pin SLED2 to avoid logic level uncertainties at this pin. Otherwise pin SLED2 can be connected directly either to ground or to the battery voltage.

**Table 3-3** Precharge Current Selection

| SLED1               | SLED2                                                                                                 | Precharge current            |

|---------------------|-------------------------------------------------------------------------------------------------------|------------------------------|

| on during precharge | pin shorted to GND                                                                                    | I <sub>Prech2</sub> (120 mA) |

|                     | pin shorted to VBAT or connected to LED's cathode                                                     | I <sub>Prech1</sub> (60 mA)  |

|                     | pin wherever connected, so<br>long as battery voltage is<br>less or equal than<br>approximately 1.2 V | I <sub>Prech1</sub> (60 mA)  |

As soon as the system has started, the precharge function can be turned off by setting bit PREOFF = 1 in register **CHCTRL2**.

To ensure system stability in case of battery removal a window comparator takes care that the precharger never raises the battery node of E-POWERlite to voltages above  $V_{PREmax}$  (see Table 5-24). If  $V_{PREmax}$  is reached the comparator will automatically turn off the precharge function.

The precharge function is turned on again as soon as the voltage goes below  $V_{PREmin.}$  This feature avoids that the voltage at the battery node gets too high no matter if there is a battery or not and it makes sure that the system does not turn on and off all the time.

## 3.8.2 Constant Current Charging

The constant current charging function is only available if the battery voltage is higher than  $V_{BATon}$ . In this case an external supply voltage applied to pin VDDCH higher than  $V_{DDCHmin}$  will turn on E-POWERlite and as a consequence power up E-GOLDlite.

Data Sheet 29 Rev. 1.1, 2005-12-15

Constant current charging can be initiated by E-GOLDlite via the I<sup>2</sup>C-bus interface by activating bit ON in the charger control register **CHCTRL1**.

The current limitation can be activated and pre-programmed by software in register **CHCTRL2**.

Note: Never program a charge current limitation which is above the internal current limitation of the AC-adapter. This may cause instability because the two current limitations could begin to fight against each other.

As soon as the sum of the internal voltage of the battery and of the voltage drop in the battery caused by the charging current exceeds the preprogrammed value  $V_{CHmax}$  the charge control circuit changes automatically to constant voltage mode. E-POWERlite can be programmed to generate an interrupt when this happens.

## 3.8.3 Constant Voltage Charging

To be able to charge Li-Ion batteries up to their full capacitance E-POWERlite provides a precisely programmable voltage limiting. The end voltages for the charging process can be programed to 3 different values of  $V_{CHmax}$ . The maximum charging voltage is selected by bits VMAX in register **CHCTRL1**. During voltage limitation, E-POWERlite will reduce the current through transistor T1 in any case, as soon as the voltage on the battery rises to the permitted maximum voltage. In this state the circuit operates like a linear regulator in regulation and constant current charging is replaced by constant voltage charging.

For Li-lon batteries a constant-voltage charging of either VCHmax1 or VCHmax2 can be chosen.

Note: Never program a V<sub>CHmax</sub> voltage which is above the maximum allowed voltage of the used battery type.

Note: For safety reasons, when using Li-lon batteries we strongly recommend to use a battery pack with a safety switch including overvoltage protection.

For NiMH batteries the maximum charging voltage is limited to  $V_{CHmax3}$ . This maximum voltage is mainly required for the protection of the E-POWERlite itself.

In continuous charging mode the E-GOLDlite controller will turn on and off the charging process. In pulse charging mode only turn-on is required. Turn-off is done automatically by E-POWERlite after a preselected time.

## 3.8.4 Pulse Charging

Pulse charging (bit PCH = 1 in register **CHCTRL1**) is usually used for top-off charging of Li-Ion and Li-Polymer batteries, when the maximum continuous charging voltage of the Li-Ion battery ( $V_{CHmax1}$  or  $V_{CHmax2}$ ) has been reached. In pulse charging mode each charging pulse has to be triggered by a command to E-POWERlite specifying the length of the charging pulse. The pulse charging mode of E-POWERlite permits generation of

Data Sheet 30 Rev. 1.1, 2005-12-15

a charging pulse of a predefined length without requiring the E-GOLDlite controller to turn off the charging process. This reduces the processing load on the E-GOLDlite controller and avoids the risk of generating a charge pulse of excessive length due to a software problem in the E-GOLDlite controller.

In pulse charging mode voltage limitation can be used in an alternative way. Bit CHMD in the charger status register **CHST** will always be reset to 0 when the voltage on pin VBATS reaches the preprogrammed level VCHmax . If bit VL in register **CHCTRL1** is set to 1 E-POWERlite will switch from constant current charging to constant voltage charging as in continuous charging mode. If bit VL in register **CHCTRL1** is set to 0 E-POWERlite will stop charging as soon as bit CHMD has been reset. If E-POWERlite has been set up appropriately (bit EICHMD=1 in register **INTCTRL1**) output pin INTOUT will toggle, signalling the change to the E-GOLDlite controller.

During pulse charging, Li-Ion batteries voltage limiting can reduce the efficiency of the pulses. By selecting the highest maximum charging voltage  $V_{CHmax3}$  full charging current is present during the charging pulse.

Note: When programming  $V_{CHmax3}$  the voltage across the battery may rise above the maximum continuous charging voltage of the Li-lon battery ( $V_{CHmax1}$  or  $V_{CHmax2}$ ) for a short time interval. See battery specs for allowed exceeding of the maximum voltage during pulse charge.

Compared to continuous constant voltage charging, the power dissipation in the external p-channel FET is significantly lower in pulse charging mode. Both the battery voltage during charging and after the end of the charging pulse may be used to control the charging process. These voltages are usually measured by the E-GOLDlite controller using the A/D converters in its measurement interface.

An overview of the functionality is given in **Table 3-4**.

Data Sheet 31 Rev. 1.1, 2005-12-15

Table 3-4 Charging Conditions and Modes

|                                         |      |     |                 | Voltage             |                     |          |               |  |

|-----------------------------------------|------|-----|-----------------|---------------------|---------------------|----------|---------------|--|

| Battery                                 | CHST |     | CHCTRL1         |                     |                     | Function | ction Limited |  |

| voltage<br>versus<br>V <sub>CHMAX</sub> | CHMD | PCH | Charg<br>e mode | Voltage<br>limit VL | Pulse timer running |          |               |  |

| V <sub>BATS</sub> <                     | 1    | 0   | cont.           | Х                   | -                   | on       | no            |  |

| $V_{CHMAX}$                             |      | 1   | pulse           |                     | no                  | off      | -             |  |

|                                         |      |     |                 |                     | yes                 | on       | no            |  |

| V <sub>BATS</sub> =                     | 0    | 0   | cont.           |                     | -                   | on       | yes           |  |

| $V_{CHMAX}$                             |      | 1   | pulse           | 0                   | Х                   | off      | -             |  |

|                                         |      |     |                 | 1                   | no                  | off      | -             |  |

|                                         |      |     |                 |                     | yes                 | on       | yes           |  |

The duration of the charging pulse can be selected by the E-GOLDlite controller in the range of about 2 ms to 262 ms with a step width of a factor of 2 by setting bits PL in register CHCTRL1. To trigger a charging pulse E-GOLDlite must send a command to register CHCTRL1 with bit ON set to 1 and pulse charge mode selected. This starts an internal counter that limits the duration of the charge pulse to the selected time interval. The charge pulse is always terminated when the time-out of the internal counter has been reached. If bit VL in register CHCTRL1 is set to 0 and the maximum charging voltage is reached it is terminated prematurely and the internal timer is reset. If E-POWERlite has been set up appropriately (bit EICHMD=1 in register INTCTRL1) output pin INTOUT will toggle signalling the premature termination of the charge pulse to the E-GOLDlite controller.

The pulse length is derived from the internal oscillator which is also used for the stepdown converter. All pulses show the same tolerance in duration as the clock frequency of this oscillator does.

A charging pulse can be terminated by software by switching back to continuous charge mode and turning off the charger.

A minimum pulse length of 512  $\mu$ s (256 internal clock cycles) will be retained under all conditions and the battery voltage will be evaluated only after this time has elapsed. Thereby instabilities of the charger immediately after turn-on will not cause any unwanted side-effects.

Data Sheet 32 Rev. 1.1, 2005-12-15

## 3.8.5 Charging Current Monitoring

Especially for Li-Ion batteries E-POWERlite offers a current monitoring function which can be programmed to generate interrupts when the charging current falls short of a certain level. This is useful for handling the top-off charging phase of Li-Ion batteries.

The appropriate current level for triggering an interrupt may be set by using the bits RVM in register CHCTRL2.

## 3.9 RTC Backup Battery Charging Function

The RTC supply voltage permits charging of a NiMH backup battery. This allows significantly longer backup intervals.

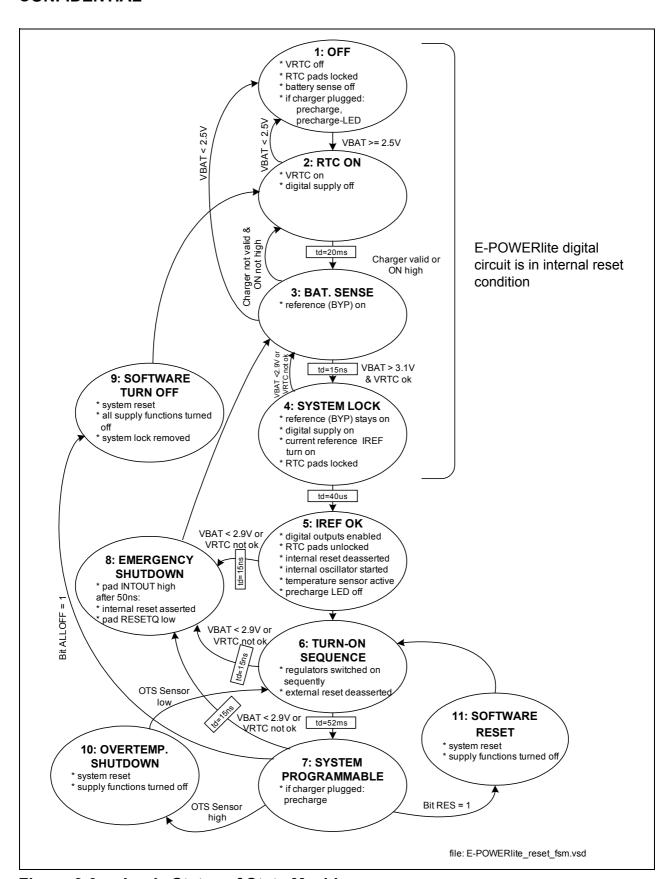

## 3.10 Power On/Off and Reset Control Logic

Under the following conditions E-POWERlite has control over the whole system:

- battery voltage is below V<sub>BATon</sub>

- · mobile phone is in shutdown mode

Control is well defined in any condition by a fixed state machine structure. The state diagram with all transitions and conditions is shown in **Figure 3-9**.

For example "State 7: System Programmable" means that E-POWERlite has started all the supply voltages needed to operate E-GOLDlite and peripherals and has initiated a proper reset sequence to the controller in E-GOLDlite.

The following chapters give a more detailled description.

Data Sheet 33 Rev. 1.1, 2005-12-15

Figure 3-9 Logic States of State Machine

Data Sheet 34 Rev. 1.1, 2005-12-15

## 3.10.1 Insertion of Battery

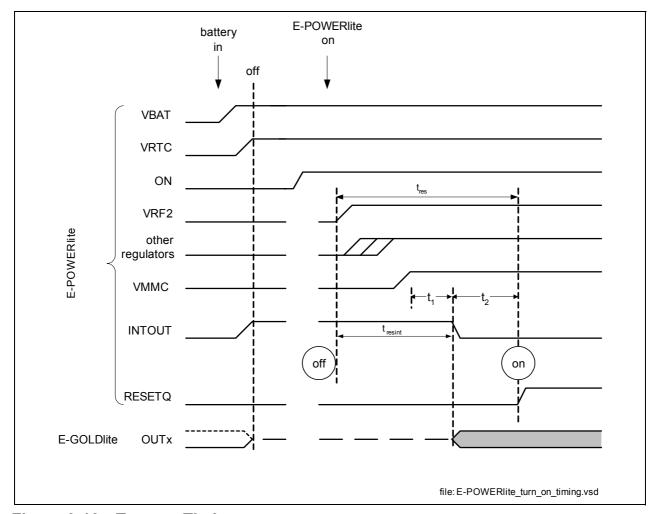

When the battery is inserted into the handset and the battery voltage  $V_{BAT}$  rises, regulator RTC is powered up. Output pin RESETQ is tied to low level and output pin INTOUT rises to high level and locks the outputs of E-GOLDlite (OUTx) into tristate (state off). Figure 3-10 shows this sequence.

#### 3.10.2 Power-down Tristate Function of E-GOLDlite

The power-down tristate function isolates the outputs of E-GOLDlite from its environment whenever no proper operation of the outputs can be guaranteed. It ensures that when the battery is inserted into the handset most output pins of E-GOLDlite are locked in tristate.

This function is controlled by pins PM\_INT and RESET\_n of E-GOLDlite. Whenever input RESET\_n of E-GOLDlite is asserted the outputs of E-GOLDlite can be put into tristate by setting input PM\_INT to high level. When input PM\_INT is at low level the outputs will show the reset values (if E-GOLDlite is powered up).

This function of E-GOLDlite is controlled by E-POWERlite via output pins INTOUT and RESETQ which have to be connected to pins PM\_INT and RESET\_n of E-GOLDlite respectively. A complete description with respect to the outputs of E-POWERlite is given in **Table 3-5**.

When E-GOLDlite is turned on, the output pins are enabled only after the core has reached its reset state. On turn-off the output pins are set to tristate prior to power-down. The outputs will remain in this state till power-up.

| RESETQ | INTOUT                  |       | E-GOLDlite Outputs State |

|--------|-------------------------|-------|--------------------------|

|        | Function                | Value |                          |

| 0      | Output tristate control | 0     | Enabled                  |

|        |                         | 1     | Disabled                 |

| 1      | Interrupt               | Х     | Enabled                  |

Table 3-5 Power-down Output Tristate Control

The detailled timing of supply voltages and control signals is described in the following sections.

#### 3.10.3 Turn-On

When E-POWERlite is in "State 2" and an on-condition appears (e.g. level on input ON is pulled to high level) the internal voltage reference (pin BYP) will start in order to determine if the battery voltage is sufficiently high to turn on the whole system. If yes E-POWERlite will reach "State 4" where the startup is continued without applying the start

Data Sheet 35 Rev. 1.1, 2005-12-15

condition any longer. The current reference (pin IREF) settles and the internal clock (about 500 kHz) and the reset counter start running.

The power-up sequence within "State 6" as listed below is controlled by the reset counter. The turn-on timing is shown in **Figure 3-10**.

- 1. The output voltages of several regulators (e.g. LRF2, SDBB, LINT) are started in intervalls shown in **Table 3-6** in order to avoid a surge and therefore a voltage drop on the battery during startup.

- 2. After the output voltages of all regulators necessary for system start-up have reached their specified value, the status RESETQ = low and INTOUT = high is kept asserted for 512 internal clock cycles ( $t_1$  = approx. 1 ms).

- 3. After that time output INTOUT is set to low to enable the outputs of E-GOLDlite.

- 4. After another 32 x 512 reset counter clock cycles ( $t_2$  = approx. 33 ms) output RESETQ goes high.

See Table for overall reset length  $t_{res}$  on RESETQ while VRF2 is running and min-max timings.

Figure 3-10 Turn-on Timing

Data Sheet 36 Rev. 1.1, 2005-12-15

# 3.10.4 Power-up Sequence

In case that the power-down tristate function as implemented in E-GOLDlite is used the power-up sequence is of minor concern since the outputs of E-GOLDlite are set to tristate as long as the system is not yet in reset state during power-up. In case no power-down tristate function is available the power-up sequence has to be kept in mind to prevent malfunction of the baseband device.

In any system the regulators should not be turned on simultaneously due to the high drain on the battery which can cause the battery voltage to drop below the operating threshold. Therefore a well defined sequence is preferable.

It is desirable to hold the core of the baseband device in reset state before enabling the I/Os. This avoids uncontrollable output signals during power-on. Inside E-GOLDlite the RESET\_n pad is part of the RTC supply domain which is always powered up. This allows to power up the baseband regulators and wait for the core to reach reset state before powering up the I/O supply regulators.

The complete Power-up sequence including the delays between the steps is shown in **Table 3-6**. Delay after sequence 2 is depending on a RC-constant, but after sequence 3, the reset counter starts operation (accuracy approx. +/- 20%). The sequence has mainly been chosen to remain compatible with E-Power and E-GOLD+. All regulators not listed in **Table 3-6** have to be turned on by software afterwards.

Table shows details for timing.

Table 3-6 Turn-on Sequence of Power Supply Functions

| Sequence | Function                                | Pin                      | Typical Time for<br>Activation of next<br>Sequence Step |

|----------|-----------------------------------------|--------------------------|---------------------------------------------------------|

|          |                                         |                          | [ms]                                                    |

| 1        | LRTC<br>INTOUT => high<br>RESETQ => low | VRTC<br>INTOUT<br>RESETQ | 0                                                       |

| 2        | BGREF                                   | BYP                      | 20                                                      |

| 3        | IREF (Reset counter started)            | IREF                     | 1                                                       |

| 4        | LRF2                                    | VRF2                     | 2                                                       |

| 5        | SDBB                                    | VDDC                     | 0                                                       |

| 6        | LBB2                                    | VBB2                     | 4                                                       |

| 7        | LBB1                                    | VBB1                     | 0                                                       |

| 8        | LINT                                    | VINT                     | 2                                                       |

Data Sheet 37 Rev. 1.1, 2005-12-15

Table 3-6 Turn-on Sequence of Power Supply Functions

| Sequence | Function                                                           | Pin    | Typical Time for<br>Activation of next<br>Sequence Step |  |  |

|----------|--------------------------------------------------------------------|--------|---------------------------------------------------------|--|--|

|          |                                                                    |        | [ms]                                                    |  |  |

| 9        | LANA                                                               | VANA   | 2                                                       |  |  |

| 10       | LSIM                                                               | VSIM1  | 2                                                       |  |  |

| 11       | LSIM2                                                              | VSIM2  | 2                                                       |  |  |

| 12       | LMMC                                                               | VMMC   | 3 (ensures t <sub>1</sub> )                             |  |  |

| 13       | INTOUT => low Internal reset sequence t <sub>resint</sub> finished | INTOUT | 33 (ensures t <sub>2</sub> )                            |  |  |

| 14       | RESETQ => high                                                     | RESETQ |                                                         |  |  |

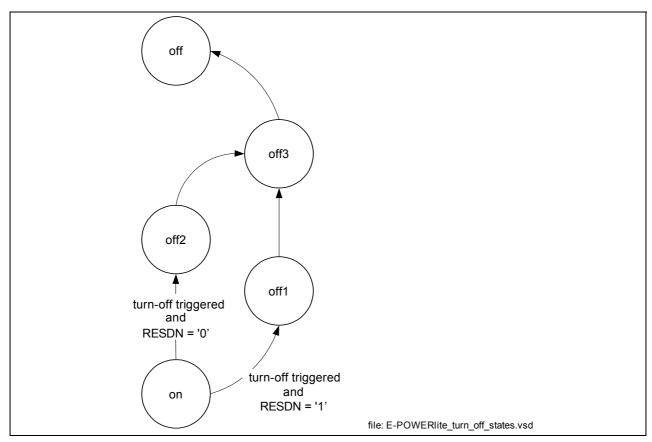

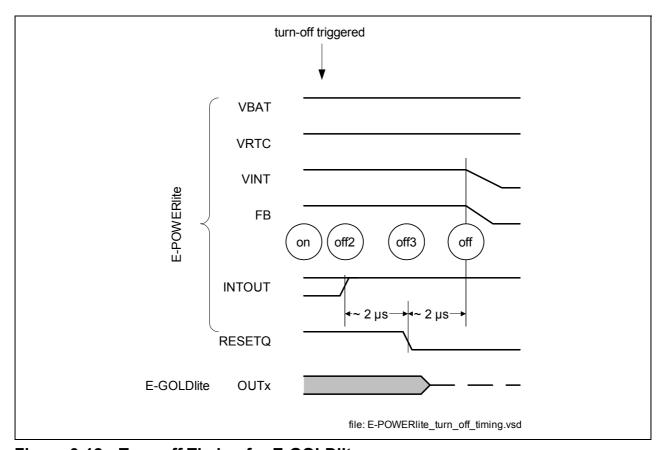

### 3.10.5 Turn-off

Turn-off is triggered by setting the ALLOFF bit in register **RESCTRL** or by an overtemperature shut-down. After a turn-off event has been triggered the signal INTOUT is pulled to high level before the supply voltages are turned off.

Output RESETQ can be handled in two different ways in the turn-off phase :

- Bit RESDN in register RESCTRL is activated:

- RESETQ is set low (reset levels are driven on the outputs of E-GOLDlite)

- After one reset counter cycle (approx. 2 μs) INTOUT is set high (outputs of E-GOLDlite are set to tristate.

- After one reset counter cycle (approx. 2 µs) all power supplies except LRTC are turned off.

- Bit RESDN in register RESCTRL is deactivated:

- · INTOUT is set high

- After one reset counter cycle (approx. 2 μs) RESETQ is set low (outputs of E-GOLDlite are set to tristate)

- After one reset counter cycle (approx. 2 µs) all power supplies except LRTC are turned off. All outputs of E-GOLDlite will retain their last state until they are set to tristate. Their levels have to be set appropriately by software. The normal interrupt input function of the E-GOLDlite PM\_INT interrupt should be disabled prior to using this function to avoid triggering interrupt handling by the assertion of output INTOUT.

The two different ways to turn-off E-GOLDlite are shown in a state diagram in **Figure 3-12**. A description of the states is given in **Table 3-7**.

Data Sheet 38 Rev. 1.1, 2005-12-15

Figure 3-11 Turn-off State Diagram

Table 3-7 Turn-off State Description

| State | Regulators | RESETQ | INTOUT          | E-GOLDlite Outputs |

|-------|------------|--------|-----------------|--------------------|

| on    | On         | Н      | X <sup>1)</sup> | active             |

| off1  |            | L      | L               | reset              |

| off2  | On         | Н      | Н               | active             |

| off3  |            | L      | П               | tristate           |

| off   | Off        | L      | Н               | tristate           |

<sup>1)</sup> normal function of output INTOUT

The timing for a turn-off sequence with bit RESDN = 0 in register **RESCTRL** is shown in **Figure 3-11**.

Data Sheet 39 Rev. 1.1, 2005-12-15

Figure 3-12 Turn-off Timing for E-GOLDlite

# 3.10.6 Undervoltage Shutdown

The normal way to shut down the system is triggered by the controller which senses the battery voltage and decides to turn off if the limit of operation is reached.

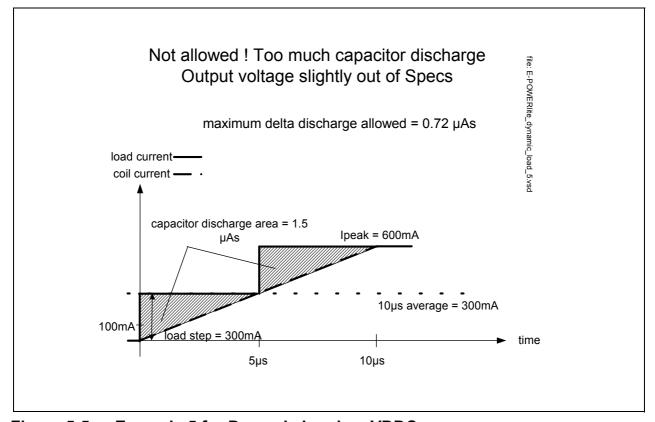

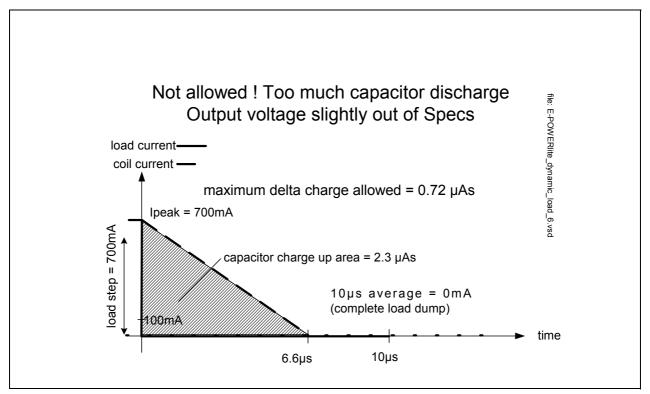

If the battery is pulled out or looses contact during full operation the capacitor in parallel to the battery which helps to avoid battery contact bouncing will be discharged in a couple of microseconds. The time for discharge depends on capacitor size, voltage level of the battery, consumers turned on etc.

In some cases the controller does not have sufficient time to program a shutdown. In this case E-POWERlite executes an undervoltage shutdown to the system because the undervoltage shutdown level is crossed (see **Table** ).

The undervoltage shutdown immediately pulls pin INTOUT to high. Approximately 50 ns later, the internal reset of E-POWERlite is triggered and RESETQ is pulled to low. This forces the E-GOLDlite outputs to tristate.