# **PMB 8753**

# BlueMoon UniCellular

BlueMoon Universal Platform

Edition 2005-11-18

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2005. All Rights Reserved.

### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

## Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

For questions on technology, delivery and prices, please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

ABM®, AOP® ARCOFI® ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®-2, SICOFI®-4, SICOFI®-4, COFI®-4, SICOFI®-4, COFI®-4, SICOFI®-4, COFI®-4, COFI®-

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

ARM, the ARM Powered logo, Thumb and StrongARM are registered trademarks of ARM Limited. The ARM logo, AMBA, ARMulator, EmbeddedICE, ModulGen, Multi-ICE, PrimeCell, ARM7TDMI, ARM7TDMI-S, ARM9TDMI, TDMI and STRONG are trademarks of ARM Limited.

The Bluetooth  $^{\mathbb{B}}$  word mark is owned by the Bluetooth SIG, Inc. and any use of this mark by Infineon Technologies AG is under license.

The BlueMoon® trade mark is owned by Infineon Technologies AG.

| PMB 8753             |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |                                                        |  |  |  |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|--|

| CONFIDENT Revision F |                                                                                                                                                                                                                                                                                                                                                                                  | 2005-11-18                                                                                                                               | T8753-XV10T9-7600                                      |  |  |  |  |  |  |

| Previous V           | ersion:                                                                                                                                                                                                                                                                                                                                                                          | 2005-06-30                                                                                                                               | T8753-XV10T8-7600                                      |  |  |  |  |  |  |

| Section              | Subjects                                                                                                                                                                                                                                                                                                                                                                         | Subjects (major changes since last revision)                                                                                             |                                                        |  |  |  |  |  |  |

| 1                    | SLEEPX                                                                                                                                                                                                                                                                                                                                                                           | moved from P1.6 (VDDPM) to P                                                                                                             | 0.15 (VDDUART)                                         |  |  |  |  |  |  |

| 1.7                  | VDDPLL                                                                                                                                                                                                                                                                                                                                                                           | VDDPLL capacitor added to figure 1.1                                                                                                     |                                                        |  |  |  |  |  |  |

| 2.3                  | Figure 2.7                                                                                                                                                                                                                                                                                                                                                                       | 7 updated with GATE_OUT and                                                                                                              | SLEEPX                                                 |  |  |  |  |  |  |

| 2.3.1                | Section u                                                                                                                                                                                                                                                                                                                                                                        | pdated to show currently offered                                                                                                         | fuse options                                           |  |  |  |  |  |  |

| 2.5                  | Text and                                                                                                                                                                                                                                                                                                                                                                         | figures updated with GATE_OUT                                                                                                            | Г                                                      |  |  |  |  |  |  |

| 3.1                  | Description                                                                                                                                                                                                                                                                                                                                                                      | ons of HCI-UART-4W and HCI TI                                                                                                            | hree-Wire UART updated.                                |  |  |  |  |  |  |

| 3.3                  | WLAN co                                                                                                                                                                                                                                                                                                                                                                          | ·                                                                                                                                        | simplified mode, data type signaling and               |  |  |  |  |  |  |

| 5.2.6.4              | PLC usag                                                                                                                                                                                                                                                                                                                                                                         | ge on eSCO packets with bit erro                                                                                                         | rs can be configured                                   |  |  |  |  |  |  |

| 6.1.2                | _                                                                                                                                                                                                                                                                                                                                                                                | Infineon_Coexistence_Enable updated Infineon_Coexistence_Set_Link_Prio added                                                             |                                                        |  |  |  |  |  |  |

| 6.1.3.2              |                                                                                                                                                                                                                                                                                                                                                                                  | FW-Variant parameter returns 0x01 for BlueMoon UniCellular in Infineon_Read_Version.                                                     |                                                        |  |  |  |  |  |  |

| 6.1.3.9              | - RSSI_N                                                                                                                                                                                                                                                                                                                                                                         | Infineon_Write_BD_DATA: - RSSI_Min and RSSI_Max default values changed - RF_Conf:Ext_PA_control changed to always zero                   |                                                        |  |  |  |  |  |  |

| 6.1.3.19             |                                                                                                                                                                                                                                                                                                                                                                                  | Bit added for configuration of PLC usage on packets with CRC errors in the ConfigBits_AIR2AUDIO parameter of Infineon_Signal_Proc_Config |                                                        |  |  |  |  |  |  |

| 6.1.3.20             | Description                                                                                                                                                                                                                                                                                                                                                                      | on of Gain parameter updated in                                                                                                          | Infineon_Gain_Setting                                  |  |  |  |  |  |  |

| 6.1.5.6<br>6.2.2.22  |                                                                                                                                                                                                                                                                                                                                                                                  | Infineon_Stimulate_Exception description updated. Infineon Fatal Exception event description updated.                                    |                                                        |  |  |  |  |  |  |

| 7                    | Electrical Characteristics - Section restructured to make it easier to find information - VDD, VDDUART and VDDPCM pads maximum supply voltage raised to 3.63V - Separate pad tables for each supply domain - Pull-up and pull-down values have been updated - Protection Circuits description has been updated - Information added about CLKIN and CLK32 inputs and requirements |                                                                                                                                          |                                                        |  |  |  |  |  |  |

| 8                    |                                                                                                                                                                                                                                                                                                                                                                                  | Information section has been res<br>kage marking, land pattern and                                                                       | structured. Information has been added solder profile. |  |  |  |  |  |  |

# **Table of Contents**

| <br> .1<br> .2<br> .3<br> .4<br> .5<br> .6                                         | Features Product Variants Functional Block Diagram Pin Configuration PG-WFSGA-65-1 Pin Configuration PG-VQFN-48-4 (Firmware Evaluation Package) Pin Description System Integration                                                          | . 11<br>. 12<br>. 12<br>. 13<br>. 14<br>. 15                 |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.3.1<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4 | Basic Operating Information Power Supply Clocking Reference Clock Low Power Clock Multiple Clock Detection Startup Fuses Low Power Modes Clock Disabling Mode Low Power Mode Ultra Low Power Mode Complete Power Down SLEEPX Configurations | . 20<br>. 21<br>. 22<br>. 24<br>. 26<br>. 26<br>. 26<br>. 27 |

| 3.1<br>3.1.1<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.1.2<br>3.1.2.1<br>3.1.2.2       | Interfaces HCI / UART Interface Supported Transport Layers HCI Three-Wire UART HCI UART-4W HCI UART-6W Low Power Mode Protocols HCI Three-Wire UART HCI UART-4W HCI UART-4W HCI UART-6W                                                     | . 30<br>. 30<br>. 31<br>. 31<br>. 31<br>. 32                 |

| 3.1.3<br>3.1.3.1<br>3.1.3.2<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3                      | UART Baud Rates Detailed UART Behavior  PCM Interface Overview PCM Pin States Sample Rate, Frame Length and PCMCLK Frequency                                                                                                                | . 43<br>. 43<br>. 44<br>. 46<br>. 47<br>. 48                 |

| 3.2.4                                                                              | Channel Start Positions                                                                                                                                                                                                                     | . 49                                                         |

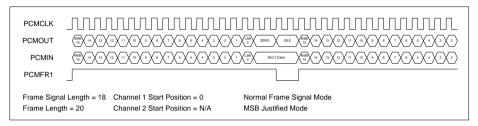

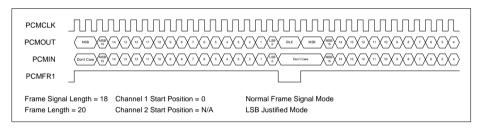

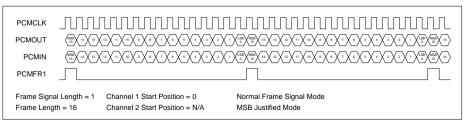

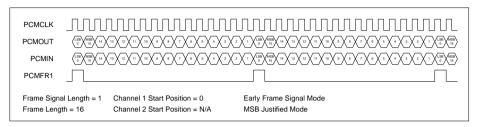

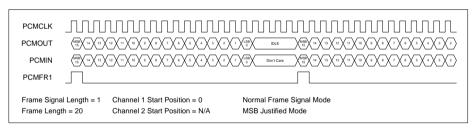

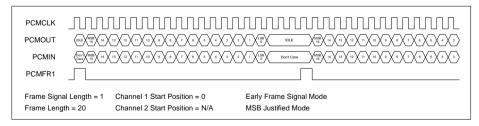

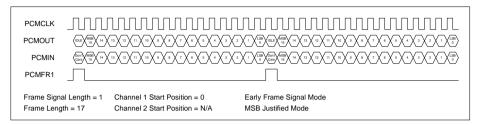

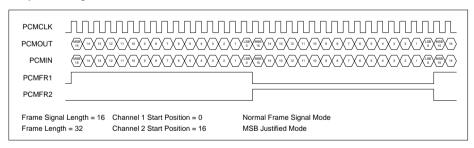

| 3.2.5<br>3.2.6   | Frame Signal Length and Justification Mode   | 49<br>50 |

|------------------|----------------------------------------------|----------|

| 3.2.7            | Early Frame Signal Mode                      |          |

| 3.2.8            | Double Clock Mode                            |          |

| 3.2.9            | Inverting PCMCLK, PCMFR1 and PCMFR2          |          |

| 3.2.10           | Enabling/Disabling Channels                  |          |

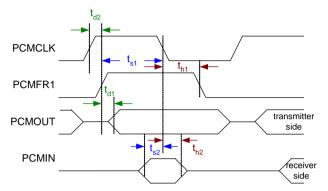

| 3.2.10           | Timing in Frame Slave Mode                   |          |

| 3.2.11           | Start and Stop of Frame Processing           |          |

| 3.2.12.1         | Clock Master Mode                            |          |

| 3.2.12.1         | Clock Slave Mode                             |          |

| 3.2.12.2         | PCM Loopback                                 |          |

| 3.2.13<br>3.2.14 | •                                            |          |

|                  | Examples for PCM Modes                       |          |

| 3.2.14.1         | Single Channel Modes                         |          |

| 3.2.14.2         | Dual Channel Modes                           |          |

| 3.3              | WLAN Coexistence Interface                   |          |

| 3.3.1            | Signals                                      |          |

| 3.3.1.1          | RF_Active                                    |          |

| 3.3.1.2          | Slot_State                                   |          |

| 3.3.1.3          | TX_Conf                                      |          |

| 3.3.2            | Pins                                         |          |

| 3.3.3            | Modes of Operation                           |          |

| 3.3.3.1          | Simplified three-wire                        |          |

| 3.3.3.2          | Standard three-wire                          |          |

| 3.3.3.3          | Standard three-wire with data type signaling |          |

| 3.3.4            | Packet Prioritization                        |          |

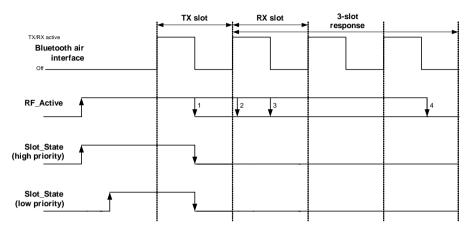

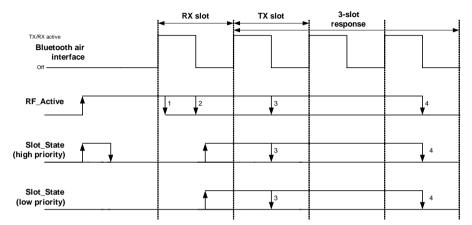

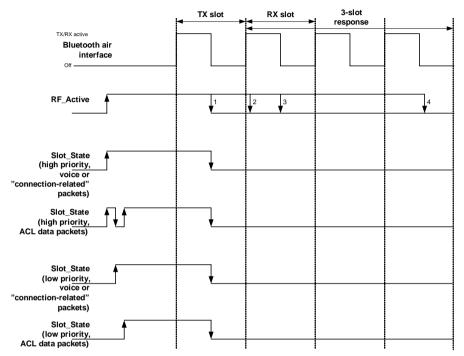

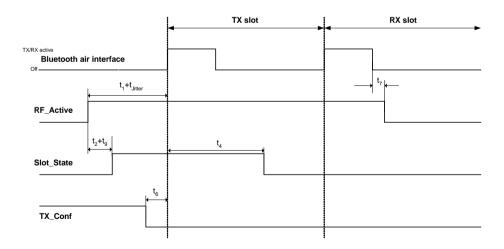

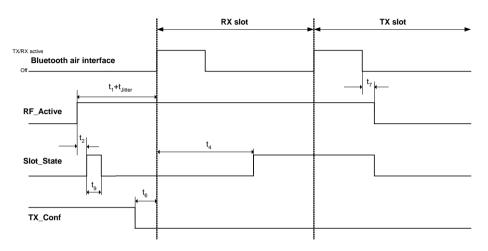

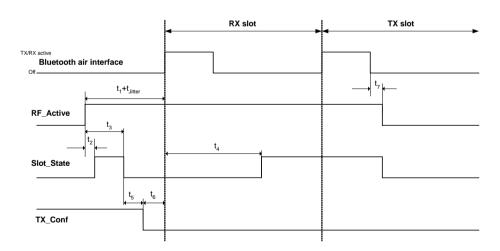

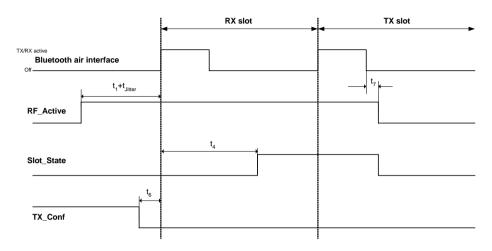

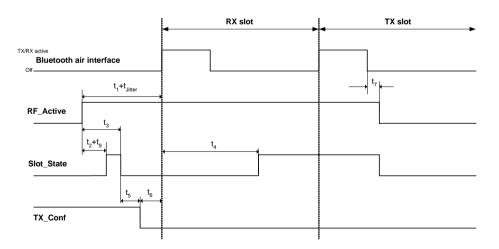

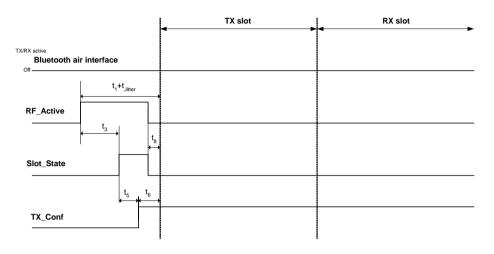

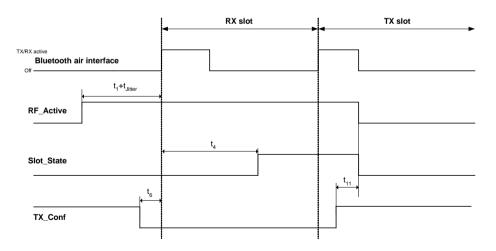

| 3.3.5            | Timing Diagrams                              | 69       |

| 3.4              | External Power Amplifier Interface           | 76       |

| 3.5              | External EEPROM / I2C Interface              | 77       |

| 3.5.1            | I2C Hardware                                 | 77       |

| 4                | General Device Capabilities                  |          |

| 4.1              | HCI+ and Bluetooth Device Data (BD_DATA)     |          |

| 4.2              | Manufacturer Mode                            |          |

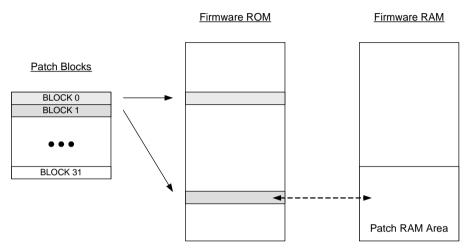

| 4.3              | Firmware ROM Patching                        | 78       |

| 4.3.1            | Patch Support                                | 78       |

| 4.3.2            | Downloading Patches                          | 79       |

| 4.3.2.1          | Patching via HCI                             | 79       |

| 4.3.2.2          | Patching via the Loader                      | 80       |

| 4.3.3            | Patching from the Host Perspective           | 80       |

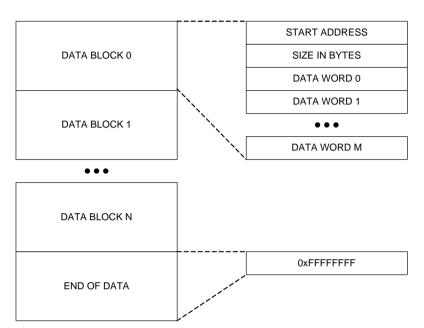

| 4.3.3.1          | Data Format                                  |          |

| 4.3.3.2          | Example Host Code                            |          |

| 4.4              | Hardware and Software Version Information    |          |

| 4.5              | Advanced Error Reporting                     |          |

| 5       | Bluetooth Capabilities                             |

|---------|----------------------------------------------------|

| 5.1     | Supported Features                                 |

| 5.2     | BlueMoon UniCellular Specifics and Extensions      |

| 5.2.1   | Configurable LMP Features                          |

| 5.2.2   | Local Device                                       |

| 5.2.2.1 | HCI Command Flow Control                           |

| 5.2.2.2 | HCI Buffers 85                                     |

| 5.2.2.3 | Event Filtering                                    |

| 5.2.2.4 | Local Name 85                                      |

| 5.2.3   | Discovery and Connection Establishment             |

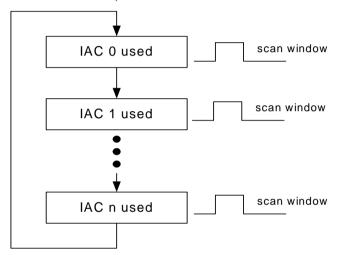

| 5.2.3.1 | Multiple Inquiry Access Codes                      |

| 5.2.3.2 | Page and Page Scan                                 |

| 5.2.4   | During Connection                                  |

| 5.2.4.1 | Scatternet and Piconet Capabilities                |

| 5.2.4.2 | Role Switch                                        |

| 5.2.4.3 | Dynamic Polling Strategy                           |

| 5.2.4.4 | Adaptive Frequency Hopping (AFH)                   |

| 5.2.4.5 | Channel Quality Driven Data Rate Change (CQDDR) 87 |

| 5.2.4.6 | Quality of Service (QoS) 88                        |

| 5.2.5   | Security                                           |

| 5.2.5.1 | Authentication                                     |

| 5.2.5.2 | Link Key Management                                |

| 5.2.5.3 | Encryption 89                                      |

| 5.2.5.4 | Pairing 89                                         |

| 5.2.6   | Synchronous Links 89                               |

| 5.2.6.1 | Interface                                          |

| 5.2.6.2 | Voice Coding                                       |

| 5.2.6.3 | eSCO                                               |

| 5.2.6.4 | Packet Loss Concealment (PLC)                      |

| 5.2.6.5 | Digital Gain Stages 90                             |

| 5.2.6.6 | Clock Drift Compensation                           |

| 5.2.7   | RSSI and Output Power Control                      |

| 5.2.7.1 | Received Signal Strength Indication (RSSI)         |

| 5.2.7.2 | Output Power Control 91                            |

| 5.2.7.3 | Ultra Low Transmit Power                           |

| 5.2.8   | Test Modes                                         |

| 5.2.8.1 | Active Tester Mode 91                              |

| 5.2.8.2 | RF Test Modes 92                                   |

| 5.2.8.3 | EDR Packet Test Command 92                         |

| 5.2.9   | Debugging 92                                       |

| 5.2.9.1 | LMP Tracing and Sending                            |

| 5.2.9.2 | Error Events                                       |

| 5293    | Information Events 93                              |

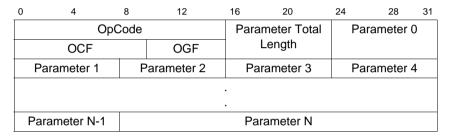

| 6        | Infineon-specific HCI Extensions (HCI+)        | . 94 |

|----------|------------------------------------------------|------|

| 6.1      | Infineon-specific HCI Commands                 | . 94 |

| 6.1.1    | Table of Infineon-specific Commands            | . 94 |

| 6.1.2    | HCI+ Interface Configuration Commands          |      |

| 6.1.2.1  | Infineon_Config_Synchronous_Interface          | . 96 |

| 6.1.2.2  | Infineon_Write_PCM_Mode                        | . 98 |

| 6.1.2.3  | Infineon_Read_PCM_Mode                         | 101  |

| 6.1.2.4  | Infineon_Write_Ports                           |      |

| 6.1.2.5  | Infineon_Read_Ports                            | 104  |

| 6.1.2.6  | Infineon_Set_Port_Bit                          |      |

| 6.1.2.7  | Infineon_Clear_Port_Bit                        |      |

| 6.1.2.8  | Infineon_Coexistence_Enable                    |      |

| 6.1.2.9  | Infineon_Coexistence_Set_Link_Prio             |      |

| 6.1.3    | HCI+ System Management Commands                | 110  |

| 6.1.3.1  | Infineon_Read_HW_Version                       |      |

| 6.1.3.2  | Infineon_Read_Version                          |      |

| 6.1.3.3  | Infineon_Enable_LPM                            |      |

| 6.1.3.4  | Infineon_Host_LPM_Start                        | 114  |

| 6.1.3.5  | Infineon_Host_LPM_End                          | 115  |

| 6.1.3.6  | Infineon_Manufacturer_Mode                     |      |

| 6.1.3.7  | Infineon_Read_Link_Quality                     |      |

| 6.1.3.8  | Infineon_Set_UART_Baudrate (M)                 | 118  |

| 6.1.3.9  | Infineon_Write_BD_Data (M)                     | 120  |

| 6.1.3.10 | Infineon_Read_BD_Data (M)                      |      |

| 6.1.3.11 | Infineon_Switch_To_Loader (M)                  |      |

| 6.1.3.12 | Infineon_Write_Ext_EEPROM_Data (M)             |      |

| 6.1.3.13 | Infineon_Read_Ext_EEPROM_Data (M)              |      |

| 6.1.3.14 | Infineon_Set_Encryption_Key_Size (M)           |      |

| 6.1.3.15 | Infineon_Read_Encryption_Key_Size              |      |

| 6.1.3.16 | Infineon_Enable_Infineon_Events (M)            |      |

| 6.1.3.17 | Infineon_Memory_Read (M)                       |      |

| 6.1.3.18 | Infineon_Memory_Write (M)                      |      |

| 6.1.3.19 | Infineon_Signal_Proc_Config                    |      |

| 6.1.3.20 | Infineon_Gain_Setting                          |      |

| 6.1.3.21 | Infineon_Get_Exception_Info (M)                |      |

| 6.1.3.22 | Infineon_Clear_Exception_Info (M)              |      |

| 6.1.3.23 | Infineon_Set_Logic_Gate                        |      |

| 6.1.3.24 | Infineon_Read_Logic_Gate                       |      |

| 6.1.4    | HCI+ Extended Bluetooth Functionality Commands |      |

| 6.1.4.1  | Infineon_TX_Power_Config                       |      |

| 6.1.4.2  | Infineon_Enable_AFH_Info_Sending               |      |

| 6.1.4.3  | Infineon_Disable_AFH_Info_Sending              |      |

| 6.1.4.4  | Infineon Set AFH Measurement Period (M)        | 155  |

| 6.1.4.5  | Infineon_Enable_CQDDR_Info_Sending                 | 156 |

|----------|----------------------------------------------------|-----|

| 6.1.4.6  | Infineon_Disable_CQDDR_Info_Sending                | 157 |

| 6.1.4.7  | Infineon_Write_Pairing_Mode                        | 157 |

| 6.1.5    | HCI+ Test Mode Commands                            | 159 |

| 6.1.5.1  |                                                    | 159 |

| 6.1.5.2  | Infineon_Activate_Deactivate_Traces (M)            | 163 |

| 6.1.5.3  |                                                    | 165 |

| 6.1.5.4  |                                                    | 168 |

| 6.1.5.5  | Infineon_Send_LMP (M)                              | 170 |

| 6.1.5.6  | Infineon_Stimulate_Exception (M)                   | 171 |

| 6.2      | Infineon-specific HCI Events                       | 172 |

| 6.2.1    | Table of Infineon-specific Events                  | 173 |

| 6.2.2    | Regular Events                                     | 174 |

| 6.2.2.1  | Infineon Startup Event                             | 174 |

| 6.2.2.2  | Infineon Default BD Data Event                     | 175 |

| 6.2.2.3  |                                                    | 175 |

| 6.2.2.4  | Infineon PTT Switch Notification Event             | 176 |

| 6.2.2.5  |                                                    | 176 |

| 6.2.2.6  |                                                    | 177 |

| 6.2.2.7  |                                                    | 177 |

| 6.2.2.8  | <u> </u>                                           | 177 |

| 6.2.2.9  |                                                    | 178 |

| 6.2.2.10 | Infineon Low Power Mode End Event                  | 178 |

| 6.2.2.11 |                                                    | 178 |

| 6.2.2.12 | Infineon Scan Status Event                         | 179 |

| 6.2.2.13 |                                                    | 179 |

| 6.2.2.14 | Infineon Activate Deactivate Traces Complete Event | 180 |

| 6.2.2.15 |                                                    | 180 |

| 6.2.2.16 |                                                    | 182 |

| 6.2.2.17 |                                                    | 183 |

| 6.2.2.18 |                                                    | 183 |

| 6.2.2.19 |                                                    | 188 |

| 6.2.2.20 |                                                    | 189 |

| 6.2.2.21 | 3 - 1 - 1                                          | 190 |

| 6.2.2.22 | •                                                  | 191 |

| 6.3      | Infineon-specific Hardware Error Event Codes       | 192 |

| 7        | Electrical Characteristics                         | 194 |

| 7.1      |                                                    | 194 |

| 7.2      |                                                    | 194 |

| 7.3      | 1 5                                                | 195 |

| 7.4      |                                                    | 196 |

| 7 4 1    | VDDSUP                                             | 196 |

| 10                     | Acronyms & Abbreviations                              | 227 |

|------------------------|-------------------------------------------------------|-----|

| <b>9</b><br>9.1<br>9.2 | Reference Schematics Reference Design Golden RF Board | 223 |

| 9                      | Reference Schematics                                  | 223 |

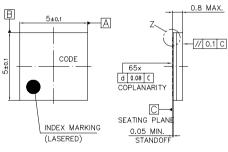

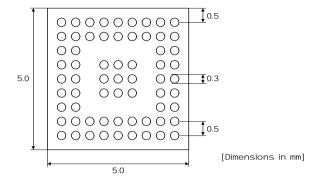

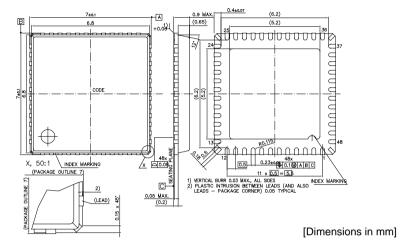

| 8.2.1                  | Package Outline                                       |     |

| 8.2                    | Firmware Evaluation Package, PG-VQFN-48-4             |     |

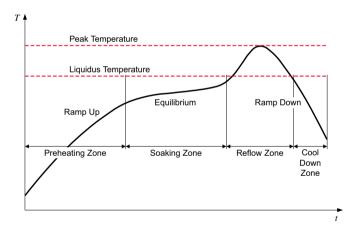

| 8.1.4                  | Solder Profile                                        |     |

| 8.1.3                  | Land Pattern                                          |     |

| 8.1.2                  | Package Outline                                       |     |

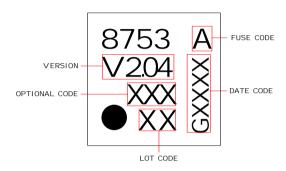

| 8.1.1                  | Package Marking                                       |     |

| 8.1                    | Production Package, PG-WFSGA-65-1                     |     |

| 8                      | Package Information                                   | 220 |

| 7.8.2.3                | RF Block Specifications                               | 218 |

| 7.8.2.2                | Customer Related Specifications                       |     |

| 7.8.2.1                | Bluetooth Related Specifications                      |     |

| 7.8.2                  | AC / DC Characteristics RF Part                       |     |

| 7.8.1                  | Operating Range RF Part                               |     |

| 7.8                    | RF Part                                               |     |

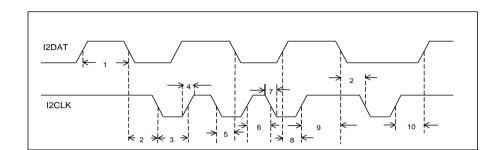

| 7.7.2                  | I2C Interface                                         | 207 |

| 7.7.1                  | PCM Interface                                         |     |

| 7.7                    | Interface Timing                                      | 204 |

| 7.6.4                  | Low Power Clock Input (CLK32)                         |     |

| 7.6.3                  | Recommended Crystal Specification                     |     |

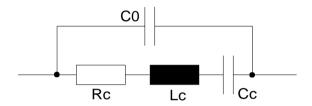

| 7.6.2                  | Crystal Oscillator                                    |     |

| 7.6.1                  | Reference Clock Input (CLKIN)                         |     |

| 7.6                    | Clock Inputs and Crystal Oscillator                   |     |

| 7.5.3                  |                                                       | 201 |

| 7.5.2                  | Pull-ups and Pull-downs                               | 201 |

| 7.5.1                  | Pad Driver and Input Stages                           | 197 |

| 7.5                    | Pads                                                  | 197 |

| 7.4.4                  | Integrated VDDRF Regulator                            | 197 |

| 7.4.3                  | Integrated VDDPM Regulator                            | 196 |

| 7.4.2                  | VDDPM                                                 | 196 |

### **General Device Overview**

## 1 General Device Overview

## 1.1 Features

#### General

- True single chip Bluetooth 2.0 + EDR solution

- Ultra low power design in 0.13 µm CMOS

- Temperature range from -40°C to 85°C

- Integrates ARM7TDMI, RAM and patchable ROM

- On-chip voltage regulators. External supply 1.8-3.6 V

- · Reference clock from internal crystal oscillator or external 10-40 MHz clock

- Low power clock from internal oscillator or external low power clock (e.g. 32.768 kHz)

- Dynamic low power mode switching with request signal for clock and power supply

#### Interfaces

- 3.25 MBaud UART with transport layer detection (HCI UART, HCI Three-Wire UART)

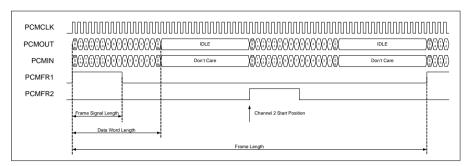

- Two-channel PCM/I2S interface for digital audio

- WLAN coexistence interface

- I2C interface for optional external EEPROM (for device configuration data)

- External PA interface for 20 dBm class 1 operation.

- General purpose I/Os with interrupt capabilities. JTAG for boundary scan and debug

- Separate voltage domains for UART and PCM interfaces

#### RF

- Transmit power programmable from -45 dBm to 6 dBm

- Receiver sensitivity typ. -90 dBm at 2Mbit/s (DQPSK)

- Integrated antenna switch

- · Integrated LNA with excellent blocking and intermodulation performance

- Low-IF receiver topology to eliminate external IF filters

- Digital demodulation for optimum sensitivity and co-/adjacent channel performance

#### Bluetooth

- · Piconet with seven slaves. Scatternet with two slave roles while still being visible

- Two simultaneous SCO/eSCO links with hardware accelerated audio signal processing

- Audio error correction algorithm (PLC) improving speech quality

- · Power control and RSSI. Hold. Park and Sniff.

- Adaptive Frequency Hopping, Quality of Service, Channel Quality Driven Data Rate

- Bluetooth security features: Authentication, Pairing and Encryption

- Bluetooth test mode and Infineon's active Bluetooth tester mode

| Туре     | Package                                |

|----------|----------------------------------------|

| PMB 8753 | PG-WFSGA-65-1                          |

| PMB 8753 | PG-VQFN-48-4 (for firmware evaluation) |

### **General Device Overview**

## 1.2 Product Variants

BlueMoon UniCellular is available in different variants and versions. Please check the corresponding errata and delta documents for the latest information.

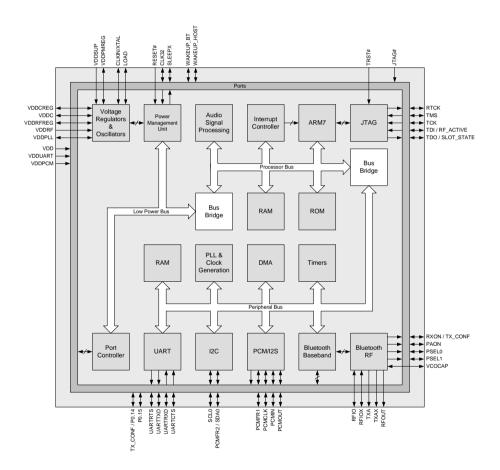

# 1.3 Functional Block Diagram

### **General Device Overview**

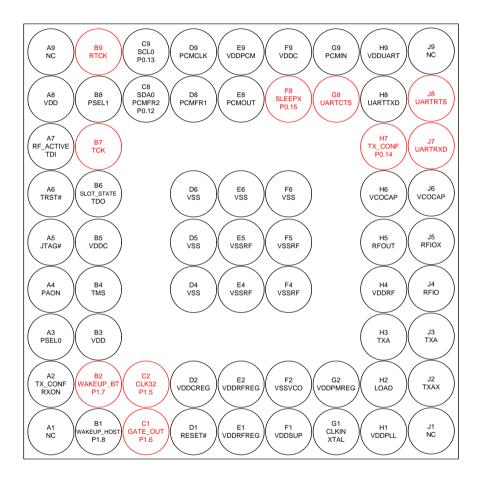

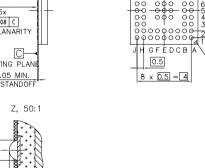

# 1.4 Pin Configuration PG-WFSGA-65-1

Red pins support wakeup functionality.

## **General Device Overview**

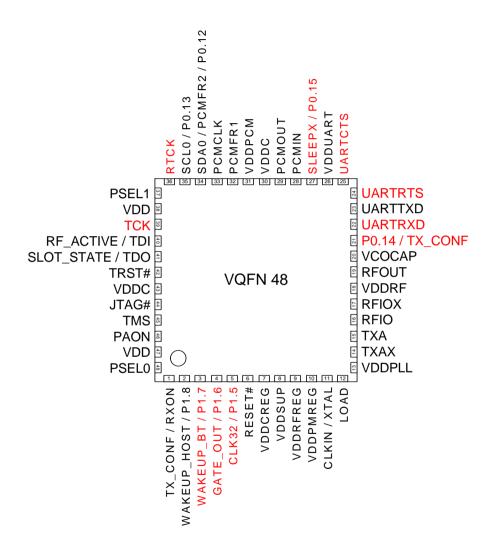

# 1.5 Pin Configuration PG-VQFN-48-4 (Firmware Evaluation Package)

Red pins support wakeup functionality.

## **General Device Overview**

# 1.6 Pin Description

| Pin No.<br>PG-VQFN-48-4/<br>PG-WFSGA-65-1 | Symbol                      | Input/<br>Output | Supply<br>Voltage | During<br>Reset  | After<br>Reset   | Function                                                            |

|-------------------------------------------|-----------------------------|------------------|-------------------|------------------|------------------|---------------------------------------------------------------------|

| 41 / B6                                   | P1.3/<br>TDO/<br>SLOT_STATE | I/O/OD           | VDD               | Z                | Z                | Port 1.3 or<br>JTAG interface or<br>WLAN coexistence interface      |

| 40 / A7                                   | P1.2/<br>TDI/<br>RF_ACTIVE  | I/O/OD           | VDD               | PU <sup>1)</sup> | PU <sup>1)</sup> | Port 1.2 or<br>JTAG interface or<br>WLAN coexistence interface      |

| 45 / B4                                   | P1.0/<br>TMS                | I/O/OD           | VDD               | PU <sup>1)</sup> | PU <sup>1)</sup> | Port 1.0 or<br>JTAG interface                                       |

| 39 / B7                                   | P1.1/<br>TCK                | I/O/OD           | VDD               | PU <sup>1)</sup> | PU <sup>1)</sup> | Port 1.1 or<br>JTAG interface                                       |

| 42 / A6                                   | TRST#                       | I                | VDD               | PD               | PD               | JTAG interface                                                      |

| 36 / B9                                   | P1.4/<br>RTCK               | I/O/OD           | VDD               | Z                | Z                | Port 1.4 or<br>JTAG interface                                       |

| 44 / A5                                   | JTAG#                       | I                | VDD               | PU               | PU               | Mode selection Port 1:<br>0: JTAG<br>1: Port                        |

| 34 / C8                                   | P0.12/<br>PCMFR2/<br>SDA0   | I/O/OD           | VDD               | PU               | PU               | Port 0.12 or<br>PCM frame signal 2 or<br>I2C data signal            |

| 35 / C9                                   | P0.13/<br>SCL0              | I/O/OD           | VDD               | PU               | PU               | Port 0.13 or<br>I2C clock signal                                    |

| 2 / B1                                    | P1.8/<br>WAKEUP_HOST        | I/O/OD           | VDD               | PD               | PD               | Port 1.8 or<br>Host wake-up signal                                  |

| 46 / A4                                   | P0.8/<br>PAON               | I/O/OD           | VDD               | PD               | PD               | Port 0.8 or<br>External PA control                                  |

| 48 / A3                                   | P0.9/<br>PSEL0              | I/O/OD           | VDD               | Z                | Z                | Port 0.9 or<br>External PA control                                  |

| 37 / B8                                   | P0.10/<br>PSEL1             | I/O/OD           | VDD               | Z                | Z                | Port 0.10 or<br>External PA control                                 |

| 1 / A2                                    | P0.11/<br>RXON/<br>TX_CONF  | I/O/OD           | VDD               | Z                | Z                | Port 0.11or<br>External PA control or<br>WLAN coexistence interface |

| 21 / H7                                   | P0.14/<br>TX_CONF           | I/O              | VDDUART           | Z                | Z                | Port 0.14 or<br>WLAN coexistence interface                          |

| 27 / F8                                   | P0.15/<br>SLEEPX            | I/O              | VDDUART           | PD               | Н                | Port 0.15 or<br>CLKIN & VDDSUP request                              |

| 23 / H8                                   | P0.4/<br>UARTTXD            | I/O/OD           | VDDUART           | PU               | PU               | Port 0.4 or<br>UART transmit data                                   |

| 22 / J7                                   | P0.5/<br>UARTRXD            | I/O/OD           | VDDUART           | Z                | Z                | Port 0.5 or<br>UART receive data                                    |

| 24 / J8                                   | P0.6/<br>UARTRTS            | I/O/OD           | VDDUART           | PU               | PU               | Port 0.6 or<br>UART RTS flow control                                |

## **General Device Overview**

| Pin No.<br>PG-VQFN-48-4/<br>PG-WFSGA-65-1 | Symbol             | Input/<br>Output | Supply<br>Voltage | During<br>Reset  | After<br>Reset   | Function                                                |

|-------------------------------------------|--------------------|------------------|-------------------|------------------|------------------|---------------------------------------------------------|

| 25 / G8                                   | P0.7/<br>UARTCTS   | I/O/OD           | VDDUART           | Z                | Z                | Port 0.7 or<br>UART CTS flow control                    |

| 32 / D8                                   | P0.0/<br>PCMFR1    | I/O/OD           | VDDPCM            | PD               | PD               | Port 0.0 or<br>PCM frame signal 1                       |

| 33 / D9                                   | P0.1/<br>PCMCLK    | I/O/OD           | VDDPCM            | PD               | PD               | Port 0.1 or<br>PCM clock                                |

| 28 / G9                                   | P0.2/<br>PCMIN     | I/O/OD           | VDDPCM            | Z                | Z                | Port 0.2 or<br>PCM data in                              |

| 29 / E8                                   | P0.3/<br>PCMOUT    | I/O/OD           | VDDPCM            | Conf.<br>PD def. | Conf.<br>PD def. | Port 0.3 or<br>PCM data out                             |

| 5 / C2                                    | P1.5/<br>CLK32     | I/O/OD           | VDDPM             | Input            | Input            | Port 1.5 or<br>LPM clock input (e.g.<br>32.768kHz)      |

| 4 / C1                                    | P1.6<br>GATE_OUT   | I/O/OD           | VDDPM             | Z                | Z                | Port 1.6 or<br>Logic gate output                        |

| 3 / B2                                    | P1.7/<br>WAKEUP_BT | I/O/OD           | VDDPM             | PD/<br>Input     | PD/<br>Input     | Port 1.7 or<br>Bluetooth wake-up signal                 |

| 6 / D1                                    | RESET#             | Al               | VDDPM             | Input            | Input            | Hardware Reset                                          |

| 13 / H1                                   | VDDPLL             | SO               | VDDPLL            | -                | inactive         | PLL digital supply (generated internally)               |

| 20 / H6, J6                               | VCOCAP             | AI/AO            | VDDRF             | inactive         | inactive         | VCO decoupling capacitor connection                     |

| 16 / J4                                   | RFIO               | AI/AO            | VDDRF             | inactive         | inactive         | LNA input, driver output                                |

| 17 / J5                                   | RFIOX              | AI/AO            | VDDRF             | inactive         | inactive         | LNA input inverted, driver output inverted              |

| 15 / H3, J3                               | TXA                | AO               | VDDRF             | inactive         | inactive         | RF class 1 PA driver output                             |

| 14 / J2                                   | TXAX               | AO               | VDDRF             | inactive         | inactive         | RF class 1 PA driver output (inv)                       |

| 19 / H5                                   | RFOUT              | AI/O             | VDDRF             | inactive         | inactive         | test pin for analog signals                             |

| 12 / H2                                   | LOAD               | А                | VDDPM             |                  |                  | With external main clock: has to be connected to ground |

| 11 / G1                                   | CLKIN /<br>XTAL    | Α                | VDDPM             | active           | active           | Main clock input                                        |

| 9 / E1, E2                                | VDDRFREG           | so               |                   |                  |                  | RF supply regulator output                              |

| 18 / H4                                   | VDDRF              | SI               |                   |                  |                  | RF supply voltage                                       |

| 47 / B3                                   | VDD                | SI               |                   |                  |                  | Supply voltage I/Os                                     |

| 38 / A8                                   | VDD                | SI               |                   |                  |                  | Supply voltage I/Os                                     |

| 26 / H9                                   | VDDUART            | SI               |                   |                  |                  | Supply voltage UART interface pads                      |

| 31 / E9                                   | VDDPCM             | SI               |                   |                  |                  | Supply voltage PCM interface pads                       |

### **General Device Overview**

| Pin No.<br>PG-VQFN-48-4/<br>PG-WFSGA-65-1 | Symbol   | Input/<br>Output | Supply<br>Voltage | During<br>Reset | After<br>Reset | Function                                                             |

|-------------------------------------------|----------|------------------|-------------------|-----------------|----------------|----------------------------------------------------------------------|

| 43 / B5                                   | VDDC     | SI               |                   |                 |                | Digital core supply pad                                              |

| 30 / F9                                   | VDDC     | SI               |                   |                 |                | Digital core supply pad                                              |

| 7 / D2                                    | VDDCREG  | SO               |                   |                 |                | Digital core supply regulator output                                 |

| 8 / F1                                    | VDDSUP   | SI               |                   |                 |                | Regulator supply input (VDDPM, VDDRF, VDDC)                          |

| 10 / G2                                   | VDDPMREG | SI/SO            |                   |                 |                | Power Management supply<br>Output on PMB8753 A<br>Input on PMB8753 J |

| - / D4, D5, D6,<br>E6, F6                 | VSS      |                  |                   |                 |                | Digital Ground                                                       |

| - / E4, E5, F4,<br>F5                     | VSSRF    |                  |                   |                 |                | RF Ground                                                            |

| - / F2                                    | VSSVCO   |                  |                   |                 |                | VCO Ground                                                           |

Fixed pull-up/pull-down if JTAG interface is selected, not affected by any chip reset. If JTAG interface is not selected the port is tristate.

## Descriptions of acronyms used in the pin list:

| Acronym | Description                          |

|---------|--------------------------------------|

| 1       | Input                                |

| 0       | Output                               |

| OD      | Output with open drain capability    |

| Z       | Tristate                             |

| PU      | Pull-up                              |

| PD      | Pull-down                            |

| Α       | Analog (e.g. Al means analog input)  |

| S       | Supply (e.g. SO means supply output) |

### **General Device Overview**

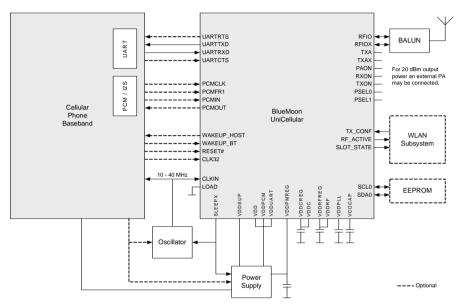

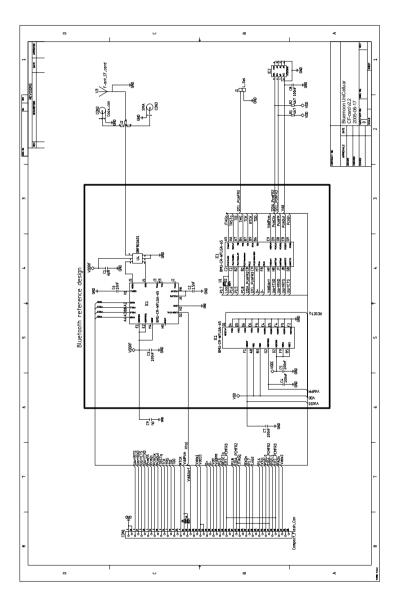

## 1.7 System Integration

BlueMoon UniCellular is optimized for cellular phone applications. It has all the required interfaces and is designed to have a low bill of material (BOM) and a small PCB size. **Figure 1-1** shows a typical application example.

Figure 1-1 Example Cellular Phone Bluetooth System

The UART interface is used for Bluetooth HCI communication between the cellular baseband and BlueMoon UniCellular. When the HCI UART transport layer is used, four interface lines are needed: two for data (UARTTXD and UARTRXD) and two for hardware flow control (UARTRTS and UARTCTS). When the HCI Three-Wire UART transport layer is used the hardware flow control lines are optional. The UART interface has its own supply voltage (VDDUART) to ensure compatibility with the I/O voltages used by the cellular baseband. In addition to the standard Bluetooth HCI commands, BlueMoon UniCellular supports a set of Infineon specific commands called HCI+.

Digital audio can either be sent over the HCI interface or over the dedicated PCM/I2S interface. The PCM/I2S interface is highly configurable and handles up to two audio channels. The interface has a separate supply voltage (VDDPCM).

Low power mode control of BlueMoon UniCellular and the cellular baseband can be implemented in different ways, either using the dedicated WAKEUP\_HOST and WAKEUP BT signals or using signaling over the HCI interface. The host can reset

### **General Device Overview**

BlueMoon UniCellular via the RESET# signal or by grounding VDDPMREG and VDDSUP. Both methods will force BlueMoon UniCellular to enter its lowest power mode.

In a cellular system, BlueMoon UniCellular can make use of available oscillators and power supplies. A low power clock can be connected to CLK32 or generated internally by a low power oscillator. A 10 - 40 MHz reference clock can be connected to CLKIN or generated by the internal crystal oscillator with a crystal connected to CLKIN and LOAD. Power can be individually supplied to the different voltage domains or supplied to the single VDDSUP input from which internal regulators can generate all required voltages.

The SLEEPX signal indicates when CLKIN and VDDSUP are needed by BlueMoon UniCellular. This can be used to switch off the external oscillator and regulators when they are not needed. SLEEPX can be configured in several ways to coexist with the cellular baseband's clock and power request signals.

An optional EEPROM for storage of Bluetooth device data (BD\_DATA) can be connected to the I2C interface. In a cellular system the device data is normally downloaded from the cellular baseband during startup and the EEPROM is not needed.

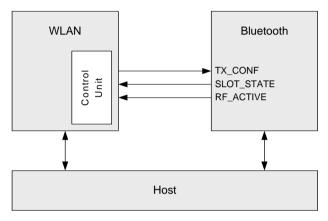

If a WLAN subsystem is collocated with BlueMoon UniCellular the WLAN coexistence interface should be used to enhance Bluetooth and WLAN performance. To coexist with external WLAN devices BlueMoon UniCellular supports adaptive frequency hopping.

The RF interface delivers enough output power for most use cases. If 20 dBm (maximum class 1 output power) is required, an external power amplifier can be connected.

## **Basic Operating Information**

# 2 Basic Operating Information

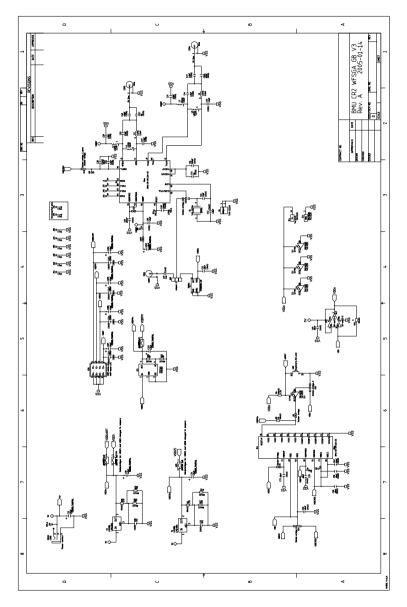

## 2.1 Power Supply

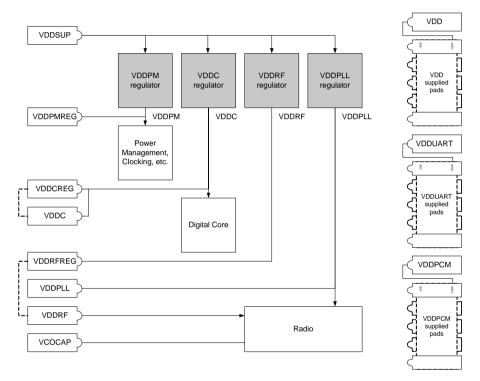

Figure 2-1 provides an overview of the power supply concept in BlueMoon UniCellular.

Figure 2-1 Power Supply Overview

VDDSUP is the main power supply for the device; it is possible to derive all other internal power supplies from this supply. Where a suitable external regulator exists, the VDDPM and/or the VDDRF supplies can be fed externally and the associated regulator disabled.

The low power supply VDDPM must always be present, which means that VDDSUP must always be supplied unless VDDPM is supplied externally. When VDDPM is supplied externally, the SLEEPX signal can be used to signal when the external VDDSUP supply can be switched off, and when it must be supplied. VDDPM must be supplied before or at the same time as any other supplies are applied. After VDDPM and

## **Basic Operating Information**

the I/O voltages (VDD, VDDUART and VDDPCM) has been supplied, VDDPM may be grounded and reapplied any number of times while the I/O voltages are present.

The main digital logic power supply, VDDC, is only present when in active mode. VDDC is derived from VDDSUP by the integrated VDDC regulator.

VDDRF is the main supply for the RF blocks in BlueMoon UniCellular. This is either generated from VDDSUP via the internal VDDRF regulator, or is supplied externally. The VDDRF regulator, when enabled, is switched on and off via internal control signals and is only on when required. VDDPLL, that is generated from VDDSUP by the VDDPLL regulator, supplies the digital parts of the PLL.

The regulator outputs should be decoupled externally. The outputs from VDDCREG and VDDRFREG should be connected to the other supply pads in the respective voltage domain (VDDC and VDDRF).

The PCM interface and the UART interface are supplied with dedicated, independent, reference levels via the VDDPCM and VDDUART pins. All other digital I/O pins are supplied by VDD. **Section 1.6** provides a mapping between pins and supply voltages.

The I/O power domains (VDDPCM, VDDUART and VDD) are completely separated from the other power domains and can stay present also in low power mode when VDDSUP, VDDC, VDDRF and VDDPLL are switched off.

## 2.2 Clocking

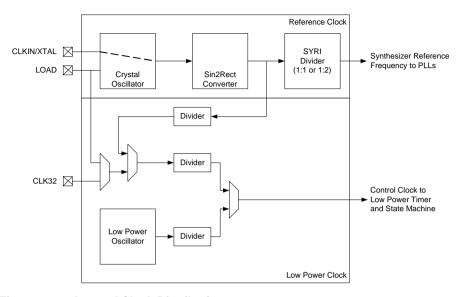

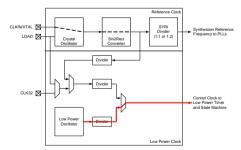

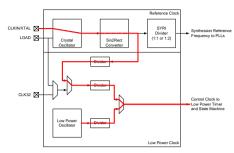

BlueMoon UniCellular requires two clocks: a reference clock and a low power clock. The reference clock is only needed when BlueMoon UniCellular is active (indicated by the SLEEPX signal) and is then used to generate clocks for main blocks like the CPU, the memories and the radio. The low power clock must always be present to keep the low power timers running and is also needed during startup. A part of the internal clock distribution is shown in Figure 2-2.

#### 2.2.1 Reference Clock

The reference clock can either be generated by the built-in crystal oscillator or provided externally. When an external clock is used, the crystal oscillator may be switched off (bypassed) to save power. The Synthesizer Reference Input (SYRI) Divider is programmable to divide by 1 or 2 to create a suitable reference frequency for the PLLs. The configurations are done with the BD\_DATA parameters *Clk\_Conf* and *Input\_Freq*.

If the crystal oscillator is used, a calibration value should be written to the BD\_DATA parameter *Osc\_Trim*. This value controls a built-in capacitance array with which it is possible to achieve a frequency accuracy of ±2 ppm.

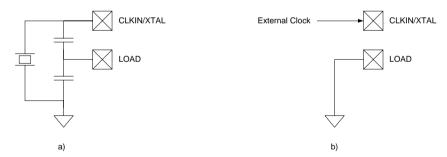

Figure 2-3 shows how to connect a crystal or an external clock.

## **Basic Operating Information**

Figure 2-2 Internal Clock Distribution

Figure 2-3 Connection of Crystal (a) or External Clock (b)

## 2.2.2 Low Power Clock

The low power clock can be generated internally by the crystal oscillator and/or the low power oscillator or provided externally. The clock path is selected with two bits in the BD\_DATA parameter *Clk\_Conf*. The following selections are possible:

## **Basic Operating Information**

## External Clock at CLK32 (Figure 2-4)

This setting should be used when an external low power clock is available. The internal low power oscillator will be disabled to save power.

## Internal Low Power Oscillator (Figure 2-5)

The internal low power oscillator is used to generate the low power clock. This setting could be used when no external clock is available.

## Reference Clock and Low Power Oscillator (Figure 2-6)

This setting makes use of the reference clock when it is available and the low power oscillator otherwise. This gives a very accurate low power clock when the reference clock is available.

Figure 2-4 Low Power Clock Selection: External Clock at CLK32

Figure 2-5 Low Power Clock Selection: Internal Low Power Oscillator

## **Basic Operating Information**

Figure 2-6 Low Power Clock Selection: Ref. Clock & Low Power Oscillator

## 2.2.3 Multiple Clock Detection

BlueMoon UniCellular can automatically detect the frequencies of external clocks for a number of scenarios. **Table 2-1** shows the combinations of CLKIN and CLK32 for which automatic detection is possible.

Table 2-1 Auto-detectable combinations of CLKIN and CLK32

| CLKIN (MHz) | CLK32 (kHz) |  |

|-------------|-------------|--|

| 12          | 32.768      |  |

| 13          | 32.768      |  |

| 14.4        | 32.768      |  |

| 16          | 32.768      |  |

| 19.2        | 32.768      |  |

| 26          | 32.768      |  |

| 26          | 96          |  |

If one of the scenarios in **Table 2-1** has been identified at startup, the UART baudrate is set to the default value 115.2 kBaud. If none of the scenarios has been identified, BlueMoon UniCellular uses the default value of the BD\_DATA parameter *Input\_Freq* and configures the baudrate to be 115.2 kBaud for a reference clock with that frequency. Multiple Clock Detection can be enabled/disabled with a bit in the parameter *Clk\_Conf*.

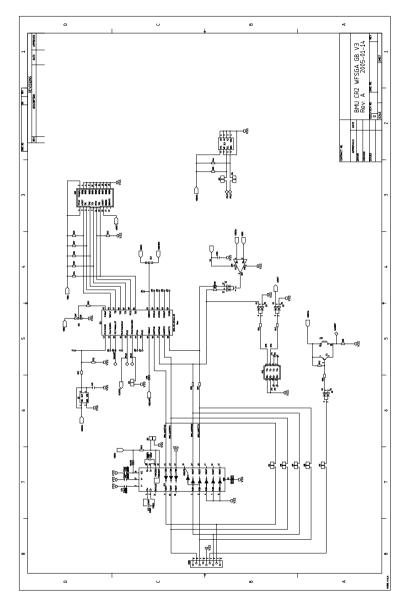

# 2.3 Startup

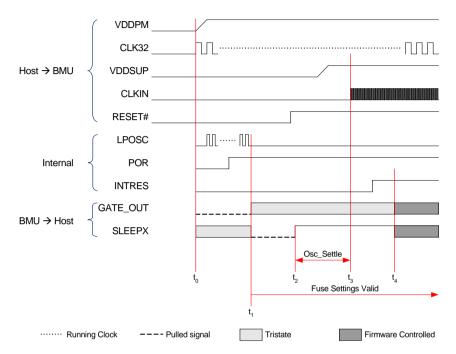

Figure 2-7 shows a typical startup sequence with external VDDPM and CLK32.

All starts at time  $t_0$  when the host switches on VDDPM and the low power clock (CLK32). Inside BlueMoon UniCellular this will cause the low power oscillator (LPOSC) and the

24

#### **Basic Operating Information**

Figure 2-7 Typical Startup Sequence

low power bandgap voltage reference to start. (If VDDSUP is available, the VDDPM regulator will also start.) When VDDPM and LPOSC are stable the internal power-on reset (POR) rises. This starts the power management state machine and initiates a read of BlueMoon UniCellular's configuration fuses.

At time t<sub>1</sub>, the fuses have been read. Depending on their state the startup procedure will continue in different ways. In the example in **Figure 2-7** the fuses cause the internal VDDPM regulator, the low power bandgap and the low power oscillator to be switched off. Detailed information is available in **Section 2.3.1**.

As long as the external RESET# is low, BlueMoon UniCellular is in its lowest power mode. When RESET# rises, the power management state machine sets SLEEPX high (at time  $t_2$ ) to request the main power supply (VDDSUP) and the reference clock (CLKIN). The state machine then waits a time (Osc\_Settle) for the external supply and clock to stabilize. When that is done, the internal reset (INTRES) to the rest of the chip rises and the firmware starts.

Note that variations of the above startup sequence are possible. VDDPM and the low power clock may for example be generated internally in which case the host must supply

## **Basic Operating Information**

VDDSUP to start the chip. If the host has the capability to switch off and ground VDDSUP and VDDPM, this can be used instead of external reset. RESET# can then be tied high.

When VDDSUP and VDDPM are grounded the outputs will be tristated. The I/O voltages VDD, VDDPCM and VDDUART may still be supplied.

## 2.3.1 Fuses

As mentioned in the previous section, BlueMoon UniCellular contains configuration fuses that define the behavior during and after reset. These fuses are programmed during chip production and cannot be changed later.

BlueMoon UniCellular is currently offered in two versions with different fuse settings. The behavior of each version is described in **Table 2-2**.

Table 2-2 Versions with Different Fuse Settings

| Version   | Description                                                                        | Remark                                                                                                                                |

|-----------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| PMB8753 A | Internal VDDPM regulator, low power oscillator and low power bandgap are enabled.  | Can be disabled by firmware depending on BD_DATA settings. Note that the fuse setting still affects the behavior while RESET# is low. |

| PMB8753 J | Internal VDDPM regulator, low power oscillator and low power bandgap are disabled. | VDDPM must be supplied externally. An external low power clock must be connected to CLK32.                                            |

#### 2.4 Low Power Modes

To minimize current consumption, BlueMoon UniCellular automatically switches between different low power modes. The major modes are described below.

# 2.4.1 Clock Disabling Mode

As soon as a part of BlueMoon UniCellular is inactive, the clocks to that part are disabled. This can be done very quickly and is done without host intervention.

#### 2.4.2 Low Power Mode

In Low Power Mode (LPM) most parts of BlueMoon UniCellular are powered down. The reference clock is still running. Entering and leaving LPM cannot be done as quickly as disabling/enabling clocks since internal state must be saved and restored, but the power consumption is lower in LPM. The minimum time of inactivity that is required to enter LPM is configured with the BD\_DATA parameter *LPM\_Threshold*.

## **Basic Operating Information**

When BlueMoon UniCellular is in LPM, HCI communication is not possible; therefore it is necessary for the host to control when LPM is allowed. The control is done via the HCI transport layer. In addition to this dynamic control, low power modes must be globally enabled. This is usually done with the HCI+ command HCI\_Infineon\_Enable\_LPM. The value <code>Default\_LPM\_Mode</code> in BD\_DATA parameter <code>LPM\_Conf</code> controls if low power modes are enabled or disabled after reset. The value <code>AutoDisable\_LPM</code> in the same parameter controls if low power modes should be disabled after host initiated wakeup.

## 2.4.3 Ultra Low Power Mode

Ultra Low Power Mode (ULPM) is similar to LPM with the addition that the reference clock may be switched off. If VDDPM is externally supplied, the main supply voltage VDDSUP may also be switched off. Bluetooth state is updated using the low power clock. Leaving ULPM takes longer time than leaving LPM because the reference clock must be started. The minimum time of inactivity that is required to enter ULPM is configured with the BD\_DATA parameter *ULPM\_Threshold*. The accuracy of the low power clock is specified with the parameter *LPM\_Drift*.

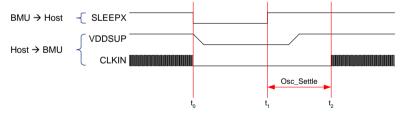

The signal SLEEPX is used to indicate when BlueMoon UniCellular enters ULPM. Figure 2-8 shows an example with the default polarity of SLEEPX. When SLEEPX goes low the system is allowed to switch off VDDSUP and CLKIN. When BlueMoon UniCellular wants to leave ULPM it sets SLEEPX high again to request VDDSUP and CLKIN. The internal low power state machine waits for a time Osc\_Settle for the power supply and clock to stabilize before starting the rest of the system. The parameter Osc Settle is configurable in BD\_DATA.

Figure 2-8 SLEEPX indicating Ultra Low Power Mode

ULPM is controlled and enabled in the same way as LPM.

## 2.4.4 Complete Power Down

If Bluetooth functionality is not needed at all, VDDSUP and VDDPM should be grounded to minimize power consumption. In this state there is no activity in BlueMoon UniCellular and the Bluetooth state (native clock, etc.) is not updated.

## **Basic Operating Information**

## 2.5 SLEEPX Configurations

The SLEEPX signal can be configured in different ways to fit with the host system's clock and power supply requests. The behavior after firmware startup can be configured with HCI+ commands and BD\_DATA parameters. The polarity of SLEEPX can be selected with a bit in the BD\_DATA parameter *BB\_Conf*. Some typical system configurations are shown below.

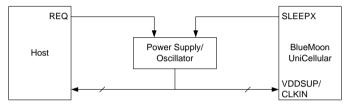

## Separate Power Supply and Clock Request Signals

The simplest case is when BlueMoon UniCellular and the rest of the system has separate signals to request power and clocks. This is shown in **Figure 2-9**.

Figure 2-9 Separate Power Supply and Clock Request Signals

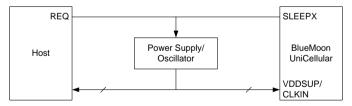

#### Shared Power Supply and Clock Request Signals

If the SLEEPX signal and the host's request signal are configured to pull in one direction and drive in the other, it is possible to wire the signals together. This is shown in Figure 2-10.

Figure 2-10 Shared Power Supply and Clock Request Signals

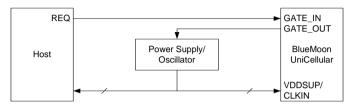

## **Gated Power Supply and Clock Request Signals**

BlueMoon UniCellular contains a programmable logic gate that can be used to combine an external request signal with the internal SLEEPX signal. The gate output is connected to the GATE\_OUT pin. The configuration is shown in **Figure 2-11**.

## **Basic Operating Information**

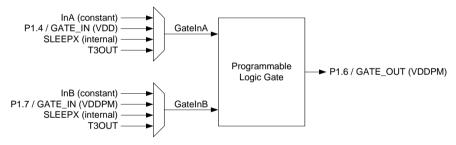

The gate is capable of performing all possible logic functions with two inputs and is supplied by VDDPM to work even when VDDSUP is not available. The configuration of input signals and logic function is done with the HCI+ command HCI\_Infineon\_Read/Set\_Logic\_Gate. The possible combinations of inputs are shown in Figure 2-12.

Figure 2-11 Gated Power Supply and Clock Request Signals

Figure 2-12 Programmable Logic Gate - Input Combinations

## 3 Interfaces

#### 3.1 HCI / UART Interface

The HCI/UART interface is the main communication interface between the host and BlueMoon UniCellular. The standard HCI commands are supported together with an Infineon specific set of commands called HCI+. The HCI+ commands are described in detail in the HCI+ section.

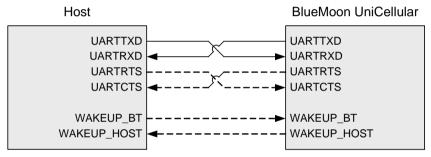

The interface consists of four UART signals and two wake-up signals as shown in **Figure 3-1**. Depending on which HCl transport layer that is used, some or all of the signals are needed.

Figure 3-1 HCI/UART Interface

# 3.1.1 Supported Transport Layers

BlueMoon UniCellular supports the HCI Three-Wire UART transport layer and two derivatives of the HCI UART transport layer (HCI UART-4W and HCI-UART-6W) where the only difference is how low power modes are handled. BlueMoon UniCellular automatically detects which transport layer that is used by the host.

## 3.1.1.1 HCI Three-Wire UART

The HCI Three-Wire UART transport layer is specified by the Bluetooth SIG. It supports error detection and retransmissions and has built-in low power mode mechanisms. Hardware flow control with UARTRTS and UARTCTS is optional. The only required signals are UARTTXD and UARTRXD (the name "Three-Wire" includes the ground connection as well).

The BlueMoon UniCellular implementation has the following characteristics:

BlueMoon UniCellular supports all features of the HCI Three-Wire UART transport layer except transmission of synchronous data packets as reliable packets.

- The time that BlueMoon UniCellular waits to receive an acknowledgement before

resending a packet can be configured with the BD\_DATA parameter Three-Wire\_

ARQ\_Timeout (in multiples of T<sub>max</sub>). The recommended value is 0x06 assuming that

the host acknowledges packets within 2·T<sub>max</sub> as recommended in the Bluetooth

specification.

- T<sub>max</sub> is defined as the time it takes to transfer 343 Bytes at the current Baud rate.

#### 3.1.1.2 HCI UART-4W

This is an implementation of the HCI UART transport layer where control of low power modes has been added using BREAK signaling on the UART lines. The four UART lines (UARTTXD, UARTRXD, UARTRTS, UARTCTS) are required.

### 3.1.1.3 HCI UART-6W

This implementation of the HCI UART transport layer uses the two wake-up lines (WAKEUP\_BT and WAKEUP\_HOST) in combination with HCI+ commands and events to handle low power modes. All six HCI/UART lines are required.

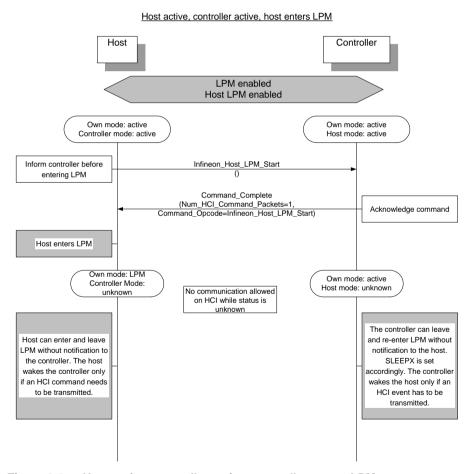

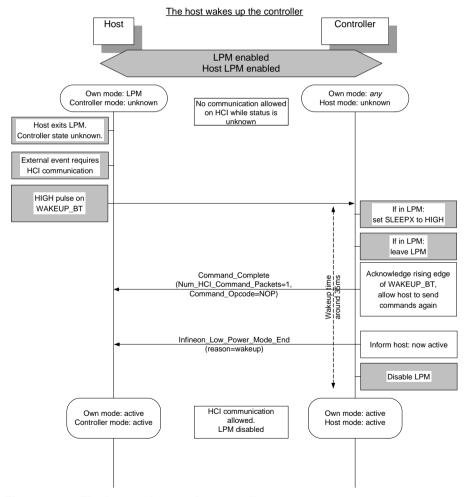

#### 3.1.2 Low Power Mode Protocols

Each HCI transport layer implements a specific low power mode protocol that can be configured in a number of ways. **Table 3-1** provides an overview of the BD\_DATA parameters, the signals, and the HCI+ commands and events that are relevant for each transport layer. Detailed descriptions of the low power mode protocols are given below.

Table 3-1 Low Power Mode Configuration Overview

| Name                    | Туре    | HCI<br>UART-4W | HCI<br>UART-6W | HCI Three-<br>Wire UART |  |

|-------------------------|---------|----------------|----------------|-------------------------|--|

| Host_LPM                | BD_DATA | X              | Х              | X                       |  |

| UART_Pulls (UARTTXD)    | BD_DATA | Х              |                |                         |  |

| UART_Invert             | BD_DATA | Х              | Х              | Х                       |  |

| Wakup_Host              | BD_DATA |                | Х              |                         |  |

| Wakeup_BT               | BD_DATA |                | Х              |                         |  |

| AutoDisable_LPM         | BD_DATA | Х              | Х              | Х                       |  |

| Infineon_Enable_LPM     | Command | X              | Х              | Х                       |  |

| Infineon_Host_LPM_Start | Command |                | Х              |                         |  |

| Infineon_Host_LPM_End   | Command |                | Х              |                         |  |

| Infineon_LPM_Start      | Event   |                | Х              |                         |  |

Table 3-1 Low Power Mode Configuration Overview

| Name                  | Туре    | HCI<br>UART-4W | HCI<br>UART-6W | HCI Three-<br>Wire UART |

|-----------------------|---------|----------------|----------------|-------------------------|

| Infineon_LPM_End      | Event   |                | Х              |                         |

| WAKEUP_HOST           | Signal  |                | Х              |                         |

| WAKEUP_BT             | Signal  |                | Х              |                         |

| Hardware_Flow_Control | BD_DATA |                |                | X                       |

| Default_LPM_Mode      | BD_DATA | Х              | Х              | Х                       |

#### 3.1.2.1 HCI Three-Wire UART

The low power mode protocol for HCI Three-Wire UART is defined in the Bluetooth specification. Only UARTTXD and UARTRXD are required.

## **Configuration and Operation Details**

The idle timeout (inactivity on the UART) before entering low power mode is 300 ms.

The BD\_DATA parameter *UART\_Pulls* has no effect when using the HCI Three-Wire UART LPM protocol. The *UART\_Invert* parameter affects UARTTXD, UARTRXD (UARTRTS and UARTCTS if enabled (default) by the *Hardware\_Flow\_Control* bit in BD\_DATA) while the controller is online<sup>1)</sup> and in LPM.

UARTRTS will stay asserted while the controller is in LPM. This makes it possible to send wake-up messages to the controller even if the host may consider the state of UARTRTS. UARTCTS will not be checked before a wake-up message is sent to the host from the controller. This makes it possible to wake up a host that cannot control its RTS to allow UART data while in for example "sleep mode".

The Infineon\_Host\_LPM\_Start and Infineon\_Host\_LPM\_End commands are not used in the HCI Three-Wire UART LPM protocol. The commands are disallowed (results in a Command Complete event with Status = "Command Disallowed"). The events Infineon Low Power Mode Start and Infineon Low Power Mode End are not used.

The Infineon\_Enable\_LPM command enables the LPM feature of the controller so it is able to enter LPM. The controller will not be able to enter LPM if the Infineon\_Enable\_LPM command has not been sent to the controller.

The AutoDisable\_LPM bit in BD\_DATA controls if the controller shall disable the LPM feature or not after the host has woken the controller. When AutoDisable\_LPM is enabled the controller will not enter LPM after being woken by the host until Infineon\_Enable\_LPM is sent and the host allows the controller to enter LPM. It is recommended to set AutoDisable\_LPM to false when using HCI Three-Wire UART.

<sup>1)</sup> Online in this section means that the controller is active i.e not in LPM

The *Host\_LPM* bit in the BD\_DATA parameter *LPM\_conf* affects the behavior of the signaling to the host during for example page scan. If activated there will be no signaling indicating autonomous wake-up of the controller (e.g. during page scan when LPM is allowed). If deactivated the controller will notify the host each time the controller wakes up autonomously.

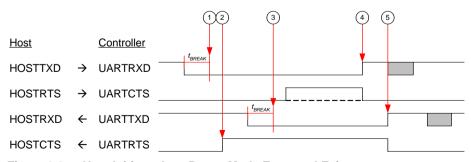

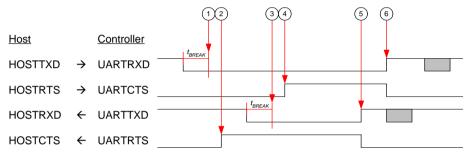

#### 3.1.2.2 HCI UART-4W

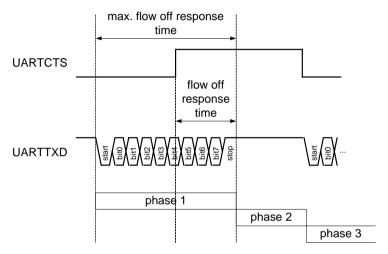

The low power mode protocol for HCI UART-4W is based on hardware signaling only. No HCI commands and events are required except Infineon Enable LPM.

The existing HCI UART signals (TXD, RXD, RTS and CTS) are used to tell the other device (host or controller) when it may enter low power mode, when it should wake up and when it cannot transmit because the first device is in low power mode.

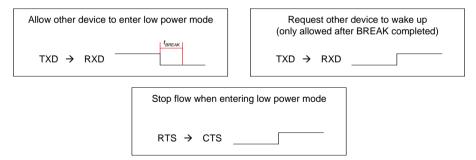

**Figure 3-2** shows the three basic signaling operations. To simplify the description it is assumed that the *UART\_Invert* bits are zero

- To allow the other device to enter low power mode, TXD is set low long enough to generate a BREAK condition in the other device's UART receiver (long enough = longer than a complete character + stop bit).

- To request the other device to wake up, TXD is set high again. This operation is only

allowed when the other device <u>has been allowed to</u> enter low power mode. It is not

required that the other device has actually entered low power mode.

- When a device enters low power mode it has to signal "flow stop" to the other device by setting RTS high.

Figure 3-2 HCI UART-4W Basic Operations (*UART\_Invert* = 0)

The BlueMoon UniCellular implementation of this protocol has the following behavior:

BlueMoon UniCellular will only allow the host to enter low power mode while it is in low power mode itself.

When requesting the host to wake up, BlueMoon UniCellular will set UARTRTS low in addition to setting UARTTXD high. This is to allow hosts that do not have interrupt capabilities on RXD to use the protocol.

## **Configuration and Operation Details**

The BD\_DATA parameter *UART\_Pulls* sets the UARTTXD level while the controller is in LPM (UARTRXD, UARTRTS and UARTCTS are not affected by the *UART\_Pulls* configuration). The level of UARTTXD during LPM, defined by the *UART\_Pulls* parameter, is not affected by the *UART\_Invert* configuration.

The *UART\_Invert* parameter affects UARTTXD, UARTRXD, UARTRTS and UARTCTS while the controller is online. The *UART\_Invert* parameter affects UARTRXD, UARTRTS and UARTCTS while the controller is in LPM.

The Infineon\_Host\_LPM\_Start and Infineon\_Host\_LPM\_End commands are not used in the HCI UART-4W transport layer. The commands are disallowed (results in a Command Complete event with Status = "Command Disallowed"). The events Infineon Low Power Mode End are not used by the controller.

The Infineon\_Enable\_LPM command enables the LPM feature of the controller so it is able to enter LPM. The controller will not be able to enter LPM if the Infineon\_Enable\_LPM command has not been sent to the controller (even if the host tries to signal enter LPM to the controller via the LPM protocol).

The AutoDisable\_LPM bit in BD\_DATA controls if the controller shall disable LPM or not after it has been woken by the host. When AutoDisable\_LPM is enabled the controller will not enter LPM after a host initiated wake-up until the Infineon\_Enable\_LPM command has been sent and the host allows the controller to enter LPM. It is recommended to set AutoDisable\_LPM to false when using HCI UART-4W.

The *Host\_LPM* bit in the BD\_DATA parameter *LPM\_conf* affects the behavior of the signaling to the host during for example page scan. If activated there will be no signaling indicating autonomous wake-up of the controller (e.g. during page scan when LPM is allowed). If deactivated the controller will notify the host each time the controller wakes up autonomously. If the *Host\_LPM* bit is activated the controller assumes that the host may be asleep and will go through the wake-up procedure including checking UARTCTS before an event can be sent to the host. If deactivated the controller assumes that the host is always ready to receive an event (only UARTCTS will be checked).

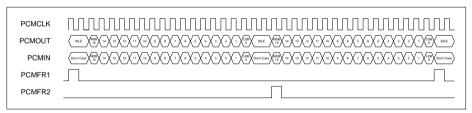

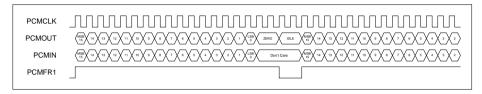

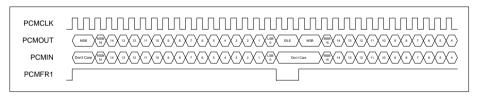

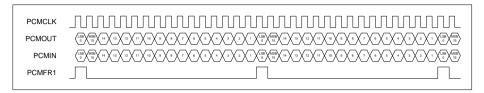

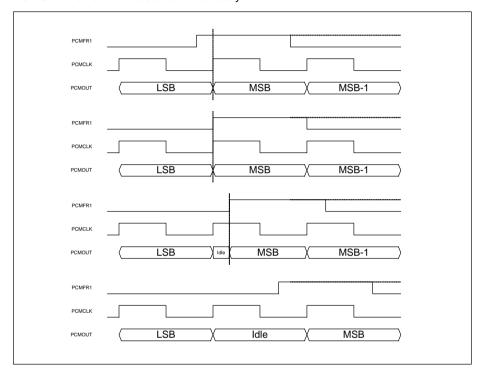

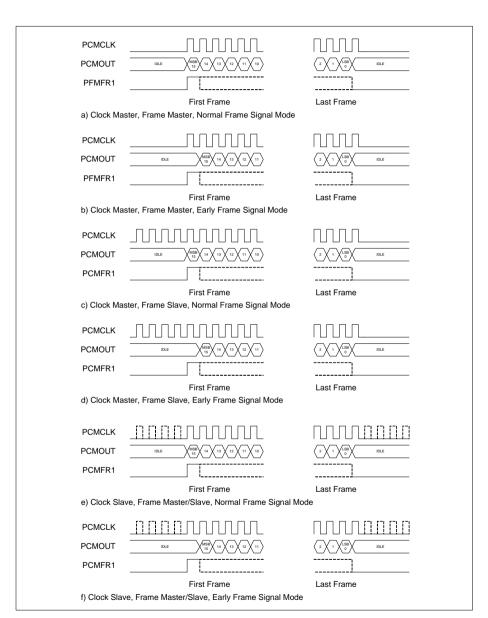

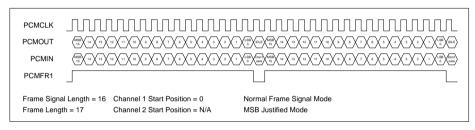

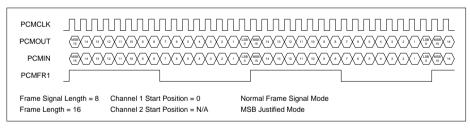

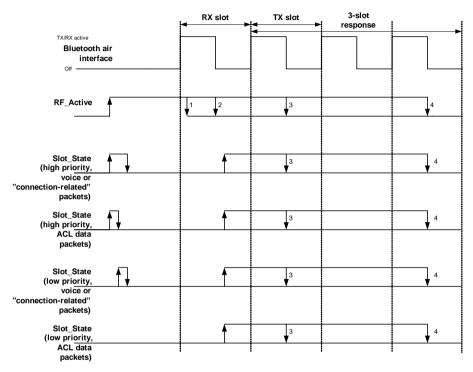

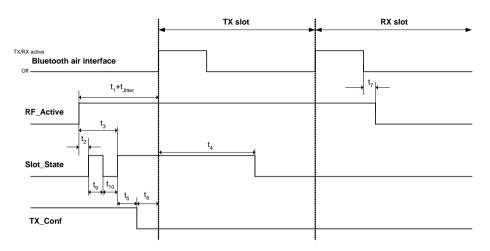

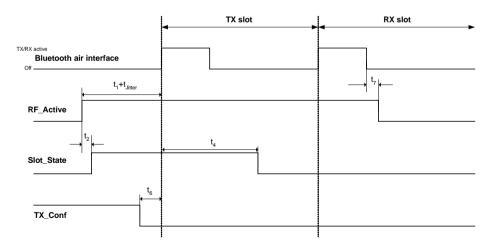

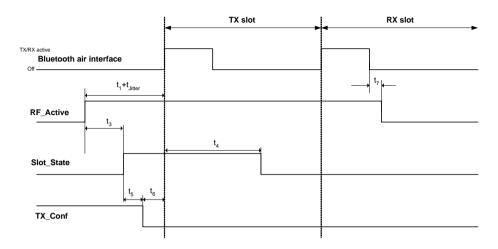

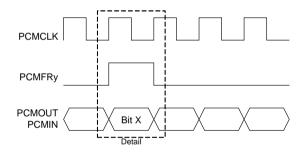

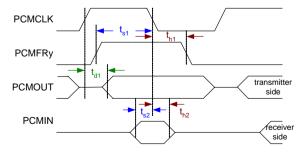

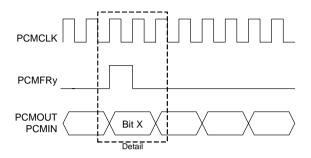

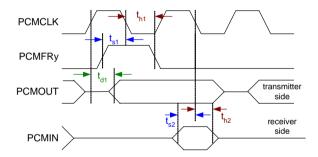

**Table 3-2** shows the signal levels on UARTTXD and UARTRTS in different modes for all combinations of *Host\_LPM* and *UART\_Pulls*. *UART\_Invert* is zero in all cases.