# How to debug SW based on C166-OSE-CMN PST

## How to debug SW based on C166-OSE-CMN PST

- Introduction

- Debugging with trace tools (Mobile Analyser)

- Real time debugging

- Types of exceptions and related breakpoints

- Logging of the exceptions

- Non-treatable crashes

- Tips on the usage of a RT debugger

#### Introduction

- To debug embedded systems comprising CMN Protocol Stack and equipped with OSE operating systems on C166based targets, several approaches can be followed.

- The first method is the inspection of standard and/or customized trace logs

- Alternatively, real time debugging shall be persued. This is useful and adviceble for the following types of bugs:

- Crash and silent reset (their occurrence can be found in the trace logs)

- Power off (silent connection loss)

The present document aims to suggest procedures and technique to debug the above-mentioned bugs. All other types of problems (e.g. analysis of function calls, system profiling, etc.) are out of the scope of the present document.

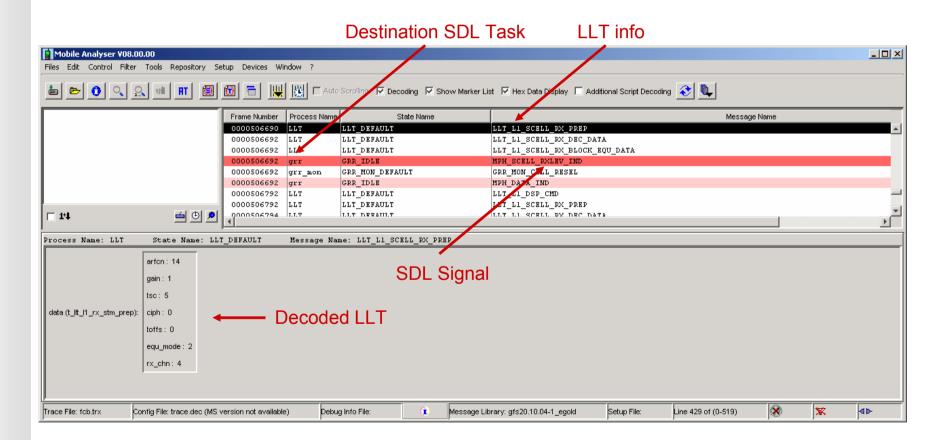

## Debugging with trace tools

- This approach helps particularly in pointing out logical faults and programming error that do not lead to a system exit.

- The MS's logs can be obtained by means of the Mobile Analyser trace tool. The tool collects (in .trx format, which can be converted to .txt) the following types of information:

- SDL signals, showing the signals and the decoded parameters, the destination tasks and their current state;

- Low Level Traces (LLT), representing the current values of L1 internal data structures (e.g. commands delivered to the DSP, data read out of the Shared Memory, the driver's events and processing, etc.). They are heavy to handle and shall be activated when necessary by selecting only the LLT groups and classes of interest with the following command

at+xl1set="L<#group> <#class1> <#class2>...L"

## Debugging with trace tools (2)

- ASCII strings, which are the result of the several "printf" instructions disseminated in the source code that can be added if required;

- Specific tasks' <u>debug signals</u>: debug signals can be built by concatenating a pseudo task ld and an event number, thus creating a structure similar to SDL signals; by sending it via the following function, a header with additional trace information (i.e. fn) is appended:

```

hwtrc_task_info(1, P_mac_db, ((P_mac_db << OS_SDL_SIGNAL_SHIFT)| debug_cause), NULL, 0);

```

In this case no parameters is used (msg=NULL). If it is required to explore a data struct, a global variable with the appropriate data type shall be included in the project and a new Message Library shall be generated.

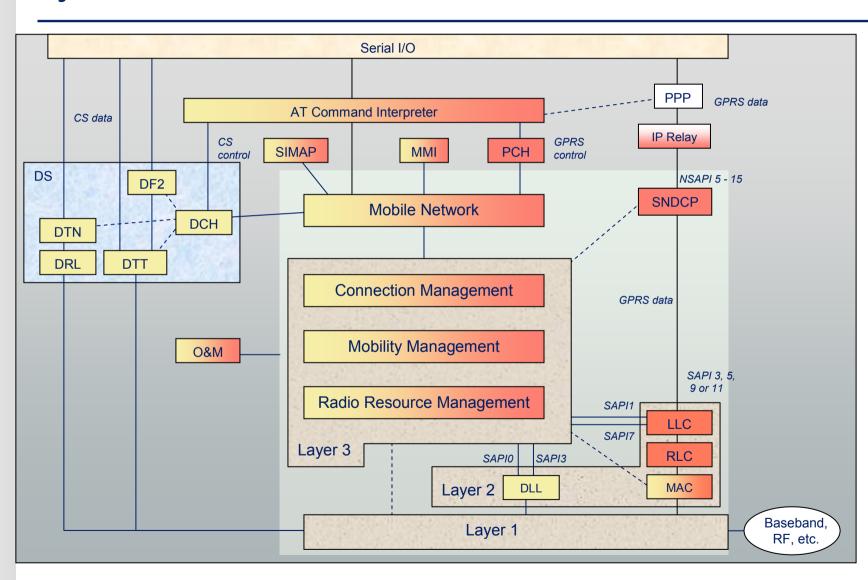

## System overview at module level

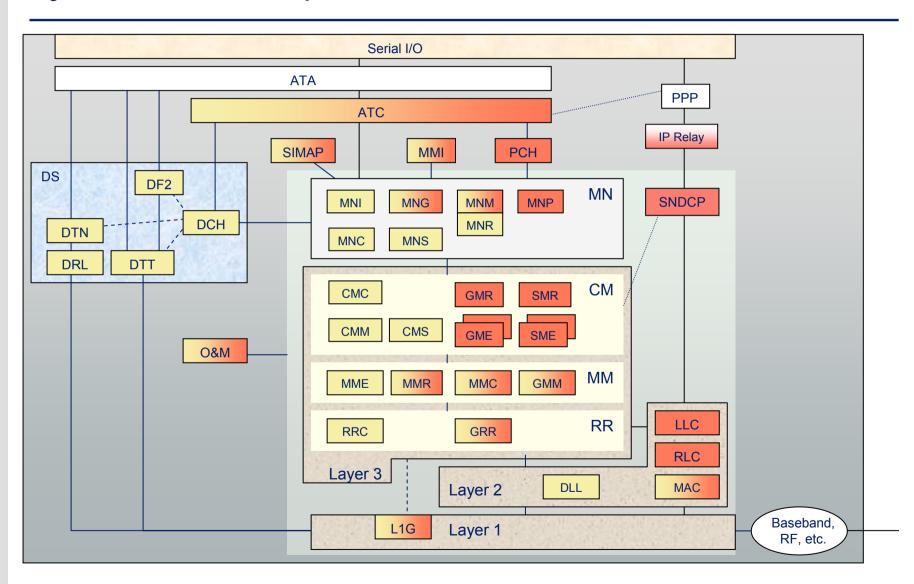

## System overview at process level

## List of processes

| ATA | ATC Adapter |

|-----|-------------|

|     |             |

ATC AT Command Interpreter

DCH Data Services Connection Handler

DTT Data Services Terminal Adapter Transparent

DTN Data Services Terminal Adapter Non-transparent

DRL Data Services Radio Link Protocol

DF2 Data Services FAX Adapter Class 2

PCH PDP Context Handler

PPP Point-to-Point Protocol

IPR IP Relay Function

SNDCP Subnetwork Dependent Convergence Protocol

MMI Man Machine Interface

SIMAP SIM Application

O&M Operation & Maintenance

MNI Mobile Network Input Manager for CC, FDN, Emerg. Call

MNG Mobile Network Registration Manager

MNM Mobile Network SMS Manager

MNR Mobile Network SMS Relay Function

MNP Mobile Network PCH Server

MNC Mobile Network Call Control

MNS Mobile Network Supplementary Services

# List of processes (2)

Layer 1 SDL Access level

| CMC | Connection Management Call Control                                          |

|-----|-----------------------------------------------------------------------------|

| CMM | Connection Management, Short Message Manager                                |

| CMS | Connection Management Call independent Suppl. Services                      |

| SMR | Connection Management, Session Manager Router                               |

| SME | Connection Management, Session Manager Entity                               |

| GMR | Connection Management GPRS SMS Router                                       |

| GME | Connection Management GPRS SMS Entity                                       |

| MME | Mobility Management: Location Registration (CS) and Idle Mode Handling (CS) |

| MMR | Mobility Management: Management of MM connection                            |

| MMC | Mobility Management: Coordination between MME and GMM, Common Functions     |

| GMM | Mobility Management for GPRS                                                |

| RRC | Radio Resource Management for Circuit Switched Mode                         |

| GRR | Radio Resource Management for IDLE Mode and GPRS                            |

| DLL | Data Link Layer                                                             |

| LLC | Logical Link Control                                                        |

| RLC | Radio Link Control                                                          |

| MAC | Medium Access Control                                                       |

L1G

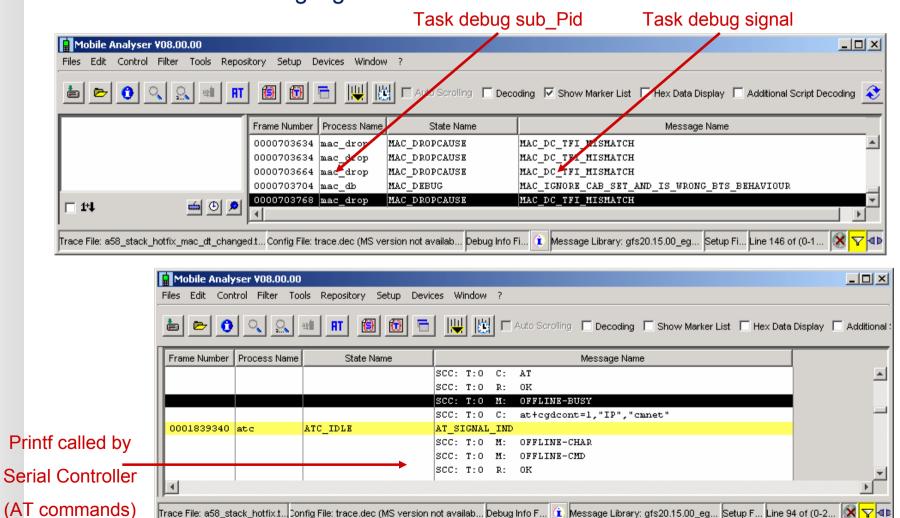

## **Examples of trace logs**

SDL signals and LLT

## Examples of trace logs (2)

Printf and task debug signals

## Real time debugging

- System crashes and system exits with power off are the most serious and tricky type of errors. There are two kinds of errors: treatable exceptions and silent crashes.

- "Treatable" exceptions are errors recognized and intercepted by the system, e.g. HW and SW traps due to wrong MCU processing, SW traps raised by the operating system, violations of asserts, explicit "exit" instructions called by the SW when a logical or procedural error condition is met.

- 2. "Silent" crashes are all system exits that cannot be numbered among the previous ones. Corruptions of the stack pointer can lead to such errors.

#### "Treatable" exceptions

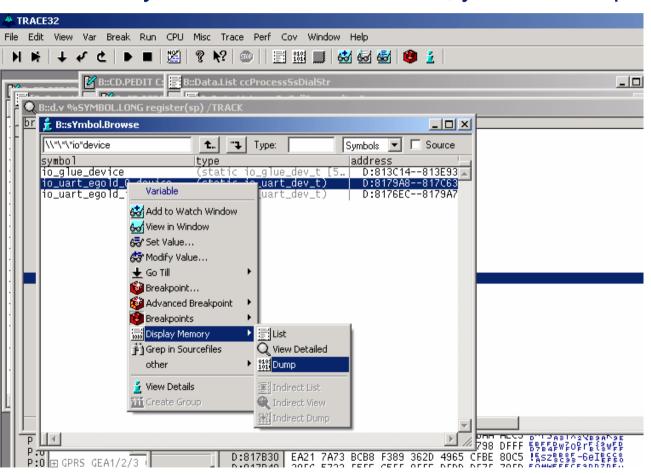

- To investigate the occurrence of a crash, an appropriate set of breakpoints shall be selected and used with the real-time debugger tool (Lauterbach).

- Once the system has halted, the tool will make some useful information available to the developer, i.e:

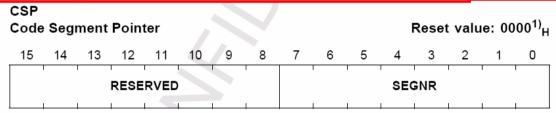

- After an exception, PSW, CSP (in segmentation mode) and IP have been pushed into the system stack. PSW, Stack Pointer and Registers are accessible via CPU→CPU Registers

- All chipset registers, available via menu/view/peripherals once the file <chipset>.per is made visible.

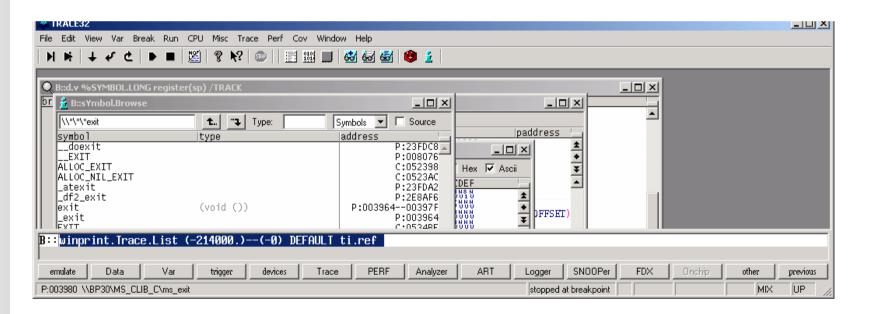

- In case the .cmm file does not provide it by default, the system stack can be inspected by entering the following command:

- d.v %SYMBOL.LONG register(sp) /TRACK

- Let's discuss the main exceptions with more detail.

## PSW, CPS, IP

1) The reset value of the bitfield segnr[1:0] is product-specific. With an alternate boot mode feature, the code execution can be started at different segments after reset.

| Field | Bits | Туре | Description                                  |  |

|-------|------|------|----------------------------------------------|--|

| SEGNR | 7:0  | rwh  | Specifies the code segment where the current |  |

|       |      |      | instruction is to be fetched                 |  |

| Field | Bits | Туре | Description                                                                                                                                     |

|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| IP    | 15:1 | rwh  | Specifies the intrasegment offset from which the current instruction is to be fetched; <b>IP</b> refers to the current segment <segnr>.</segnr> |

|       |      |      | Note: IP is always word-aligned.                                                                                                                |

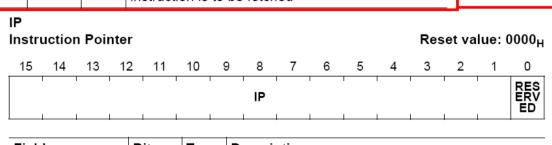

#### Software traps

- The TRAP instruction is used to cause a software call to an ISR. The trap number that is specified in the operand field of the trap instruction determines which vector location of the vector table will be used.

- The TRAP instruction's effect is similar to that of an interrupt request that uses the same vector. **PSW**, **CSP** and **IP** are pushed into the system stack and then a jump is taken to the specified vector location.

- SW traps and invoked by setting the NMI flag:

```

void TRAP_envoke_sw_trap( unsigned int id_number)

{  exception_id_number = id_number;

TFR |= TRAP_NMI; /* Envoke the Non Maskable Interrupt Trap flag */

}

```

■ This function is called by ms\_exit and ose\_exception\_handler.

#### ms\_exit

■ This function is called by all error conditions raised by the SW. In particular, it is called by ms\_severe\_exception (all tasks of the stack) and by ms\_error (L1 specific) only when:

```

if( severity <= ms_error_severity )

ms_severe_exception( line_number, filename, error_code );</pre>

```

■ There are 3 levels of the **severity** parameters of ms error:

```

#define MS_ERROR_SEVERE 0

#define MS_ERROR_LOCAL 1

#define MS_ERROR_WARN 2

```

- Debug versions are released with ms\_error\_severity set to 3.

- In case TRAP\_HANDLING is not defined, expicit calls to ms\_exit by the source code are substituted by occurrences of exit(0), which later calls ms\_exit as well.

```

#ifdef TRAP_HANDLING

ms_exit(i2_filename,i1_line_number,i3_error_code);

#else

exit (0);

```

#### ms\_exit (2)

- When you debug MMI or high level task in a step by step fashion or using SW breakpoints that introduces delays in the system executions, you affect the timings of the Layer 1. This often leads to system exits due to timings violations, e.g. the so called frame overruns.

- To prevent calls to ms\_exit when such warnings are produced, the global variable ms\_error\_severity shall be set to 0.

- This can be achieved:

- by modifying its value in file system-build\make\makeoptions.mkSYSTEM\_DEFS += MS\_ERROR\_SEVERITY=0

- runtime, by changing it with the real-time debugger once the system has halted.

- runtime, by entering the following command at+xl1set="sev0"

#### Ose\_exception\_handler

- This is the error function called by OSE operating system when an unrecoverable error occurs.

- In order to distinguish the kind of error for debugging purposes, the following variable (symbol) can be tracked with the debugger: **ERR\_MSG**.

- In particolar (see OSE manuals\Ec166KrnRM3 0.pdf)

```

switch(ERR MSG[0]) {

```

case 0x02: //The memory pool was empty when the designated process tried to allocate memory.

case 0x03: //The designated process called FREE providing a NIL-pointer

case 0x1E: //Internal stack overflow. The internal stack for designated process is too small. Increase the internal stack size in os166.con

case 0x3C: //Interrupt occurred from a source that has no process associated with it. To get the trap number subtract the value pointed to by (stackpointer+4) by 4 and then divide it with 4.

## Hardware traps

- To summarize, we have 3 exception categories:

- Software raised exceptions and software generated traps (already discussed),

- Hardware (EGL/EGR) detected abnormalities (HW traps).

- Hardware traps are issued by faults or specific system states that occur during runtime.

- When a hardware trap condition has been detected, the MCU branches to the related trap vector location and a TRAP instruction is injected into the pipeline:

- Push PSW, CSP and IP onto the system stack

- Set the **PSW** to the highest priority level, which disables all interrupts

- Branch to the trap vector location specified by the trap number

- Hardware traps are not-maskable and always have a higher priority than any other MCU task.

## Hardware traps (2)

- The C166S distinguishes eight different hardware trap functions, collected in 2 classes.

- Class A traps (same trap priority, individual vector address):

- External NMIs

- Stack overflow

- Stack underflow

- Software Break.

- Class B traps (same interrupt vector, trap identified by **TFR**):

- Undefined opcode

- Protection fault

- Illegal word operand access

- Illegal instruction access

- Illegal external bus access.

## Hardware traps (3)

# Hardware traps (4)

| Table 6-7 Hardware Traps    |           |             |                 |                  |  |  |  |  |

|-----------------------------|-----------|-------------|-----------------|------------------|--|--|--|--|

| Exception Condition         | Trap Flag | Trap Vector | Trap<br>Number  | Trap<br>Priority |  |  |  |  |

| Reset Functions:            |           |             |                 |                  |  |  |  |  |

| Hardware Reset              |           | RESET       | 00 <sub>H</sub> | IV               |  |  |  |  |

| Software Reset              |           | RESET       | 00 <sub>H</sub> | IV               |  |  |  |  |

| Watchdog Timer Overflow     |           | RESET       | 00 <sub>H</sub> | IV               |  |  |  |  |

| Debug Trap                  | DEBUG     | DEBTRAP     | 08 <sub>H</sub> | III              |  |  |  |  |

| Class A Hardware Traps:     |           |             |                 |                  |  |  |  |  |

| Non-Maskable Interrupt      | NMI       | NMITRAP     | 02 <sub>H</sub> | II.3             |  |  |  |  |

| STacK OverFlow              | STKOF     | STOTRAP     | 04 <sub>H</sub> | II.2             |  |  |  |  |

| STacK UnderFlow             | STKUF     | STUTRAP     | 06 <sub>H</sub> | II.1             |  |  |  |  |

| Class B Hardware Traps:     |           |             |                 |                  |  |  |  |  |

| UNDefined OPCode            | UNDOPC    | BTRAP       | 0A <sub>H</sub> | 1                |  |  |  |  |

| PRoTection FauLT            | PRTFLT    | BTRAP       | 0A <sub>H</sub> | 1                |  |  |  |  |

| ILLegal word Operand Access | ILLOPA    | BTRAP       | 0A <sub>H</sub> | 1                |  |  |  |  |

| ILLegal INstruction Access  | ILLINA    | BTRAP       | 0A <sub>H</sub> | 1                |  |  |  |  |

| ILLegal external BUS access | ILLBUS    | BTRAP       | 0A <sub>H</sub> | 1                |  |  |  |  |

#### TRAP\_class\_a\_handling

- External NMIs: any transition of the NMI flag bit leads to the invocation of the trap function TRAP\_class\_a\_handling

- Stack overflow/Stack underflow: whenever the stack pointer (SP) is de/incremented to a value less/more than the value in the stack overflow/underflow registers STKOV/STKUN; in CSTART:

```

MOV STKOV, #?SYSSTACK_BOTTOM + 6*2 ;Set stack underflow pointer

MOV STKUN, #?SYSSTACK_TOP ;Set stack overflow pointer

```

- **Software Break**: related to JTAG debugging features

- Class A traps cannot interrupt an atomic/extend sequence.

#### TRAP\_class\_b\_handling

- UNDefined OPCode Trap (UNDOPC): the current instruction decoded by the MCU does not contain a valid C166S opcode.

- PRoTection FauLT Trap (PRTFLT): whenever one protected instruction (e.g. EINIT end of initialization, IDLE power down CPU, SRST SW reset) is executed, the TFR.PRTFLT flag is set and the MCU enters the protection fault trap routine.

- ILLegal word OPerand Access Trap (ILLOPA): a word operand read or write access is attempted to an odd byte address.

- ILLegal INstruction Access Trap (ILLINA): a branch is made to an odd byte address.

- ILLegal external BUS access Trap (ILLBUS): the MCU requests an external instruction fetch or a data read or write and no external bus configuration has been specified.

- Class B traps can interrupt an atomic/extend sequence.

## TRAP handling

The trap interrupt vectors (4 bytes) are located in file prolog.scf.in:

```

CLASSES('TRAP_CLASS_A_NMI' (0000008h TO 0000008h UNIQUE))

CLASSES('TRAP_CLASS_A_STO' (0000010h TO 0000013h UNIQUE))

CLASSES('TRAP_CLASS_A_STU' (0000018h TO 0000018h UNIQUE))

CLASSES('T32_TRAP_CLASS' (0000020h TO 0000023h UNIQUE))

CLASSES('TRAP_CLASS_B' (0000028h TO 0000028h UNIQUE))

```

and are described in prolog debug.asm:

```

sNMIJMPSINT SECTION CODE WORD 'TRAP_CLASS_A_NMI'

pNMIJMPSINT PROC NEAR

JMPS   _TRAP_class_a_handling

RETV

pNMIJMPSINT ENDP

sNMIJMPSINT ENDS

sSTOJMPSINT SECTION CODE WORD 'TRAP_CLASS_A_STO'

pSTOJMPSINT PROC NEAR

JMPS   _TRAP_class_a_handling

RETV

pSTOJMPSINT ENDP

sSTOJMPSINT ENDP

```

## TRAP handling (2)

- All other interrupt vectors are described in os166.src → see next slide

- Both TRAP\_class\_a\_handling and TRAP\_class\_b\_handling end with the SRST instruction if SILENT\_RESET is defined.

- For TRAP handling you can also refer to document by DWD How2Debug\Trap Exception presentation.pdf

## Interrupt handling (os166.src)

```

OS166 V 43(50) SECTION CODE AT 010Ch+00h (@200)

DB

0FAh

SEG ZZ I 43

DB

DW SOF ZZ I 43

OS166 V 43 ENDS

PUBLIC l1x lisr1 actions

l1x_lisr1_actions_ EQU DATA8 14

OS166_VC_43 SECTION CODE WORD PUBLIC 'OSE_C'

OS166_VCR_43 PROC NEAR

ZZ I 43:

ATOMIC #3

SCXT DPP2, #PAG DPP2 LARGE

SCXT DPP0, #PAG BASE_DPP0

M DC, #010h

SCXT

MDH

PUSH

PUSH

MDL

SEG _l1x_lisr1_actions, _l1x_lisr1_actions

CALLS

```

## epAllOff

- Sometime the system cannot boot and switches off.

- In order to verify whether the power off is abnormal, you can set a BP at **epAllOff** function, which may be called by OMS in case of exceptions in the power-on sequence, for example if not all drivers have correctly indicated their initialization to MMI.

## Trap::Assertion

- APOXI and MMI are disseminated with ASSERT(cond) instruction, which checks that the condition <cond> holds.

- If the check fails, depending on the define APOXI\_ENABLE\_ TRAP\_INFO\_SCREEN, the system can either display the filename and line where the error occurred or call **ms\_exit** (eventually a silent reset can be trigger via SRST instruction).

## Logging of exceptions

- All "treatable" or intercepted exceptions are (should be) stored to a predefined area in the EEProm and can be read/cleared using Phonetool.

- If TRAP\_HANDLING is defined, the same memory area can host also non-unrecoverable error conditions (e.g. warnings and errors whose severity is lower than the mimimum tolerable one), which are stored by means of the function:

- void TRAP\_store\_exception(unsigned int id\_number, unsigned char log\_data\_size, void \*log\_data);

- This function can be used anytime an exception has to be stored in the *exception store* structure. This store will be transferred to NVRAM at traps or at drivers deactivation during power down.

- Please note that not all traps stored to EEP correspond to system crashes.

# Logging of exceptions (2)

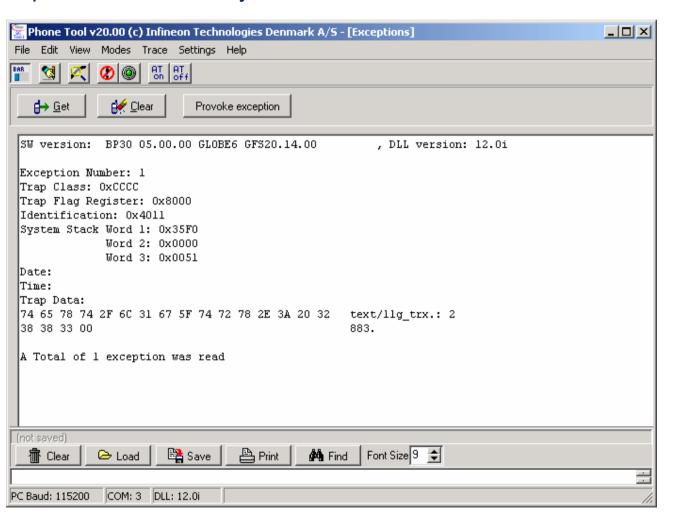

Exception list obtained by Phonetool

## Logging of exceptions (3)

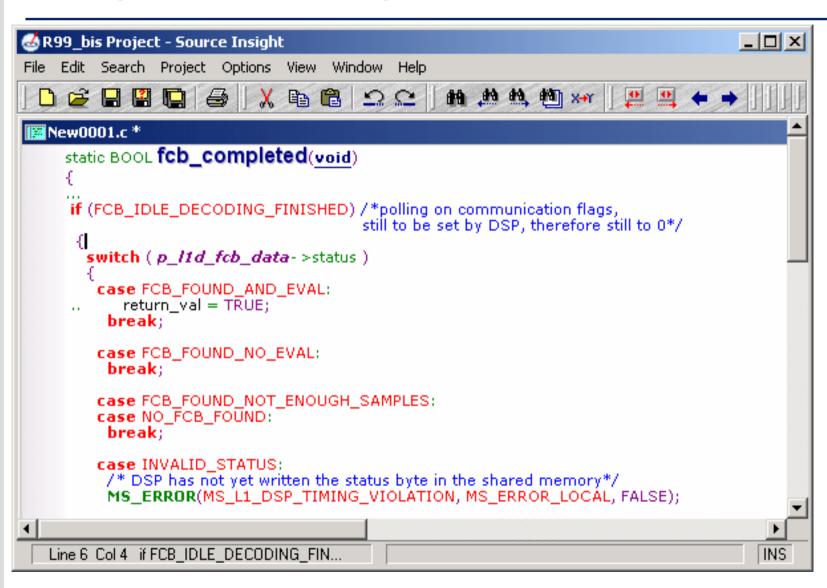

Examples of warning and errors in the source code of L1

#### Warnings:

```

if (pdch_rx_tx.deact_flg)

{

/* re-activation not allowed before deactivation is confirmed */

MS_ERROR( MS_L1_STM_PREPARE_FAIL, MS_ERROR_WARN, FALSE );

return;

}

Local error:

else

MS_ERROR( MS_L1_STM_PREPARE_FAIL, MS_ERROR_LOCAL, FALSE );

Severe error:

if (lld_fcb_stm_in_use() || lld_sb_stm_in_use() )

MS_ERROR( MS_L1_STM_FAULT, MS_ERROR_SEVERE, FALSE );

```

## Logging of exceptions (4)

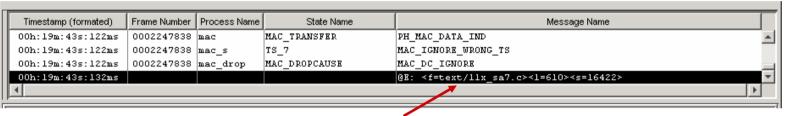

The trace logs indicate that an exception occurred by printing some information at the end of the trace.

File and line

■ If the error severity is set to 0 (i.e. only severe exceptions lead to ms\_exit), L1 warnings are traced with a LLT message:

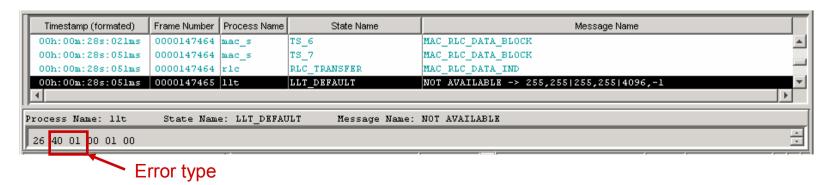

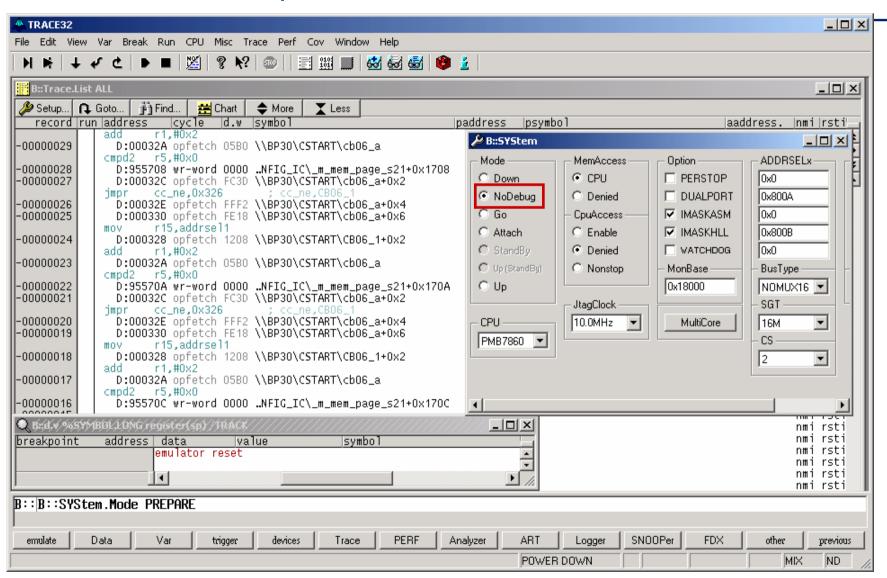

#### Non-treatable exceptions: Connection lost

■ When no BP is available for debugging, the DUT goes to "connection loss" state. In this case you have two options:

- 1. Pre-requisite: have the Power Trace connected

- 2. Select "CPU→System Settings→No debug" and then "Trace→List→All": the backtrace will be populated!

## Non-treatable exceptions: Connection lost (2)

## Non-treatable exceptions: Connection lost (3)

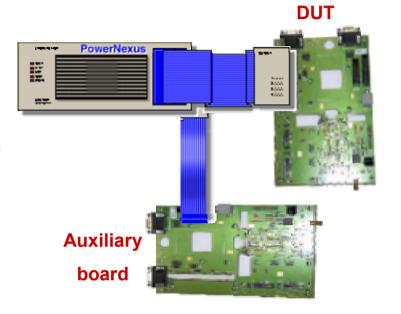

- 2. Connect the Power Trace to the DUT and the JTAG to another board.

- Make sure you are using the .abs file of the version loaded on the DUT

- When the DUT crashes, stop the auxiliary board and look to the backtrace.

This approach is useful to trace DUT in power saving mode, because it prevents the JTAG connector from keeping the MS awaken and lengthens the temporal duration of the backtrace (which is otherwise ca 2 seconds).

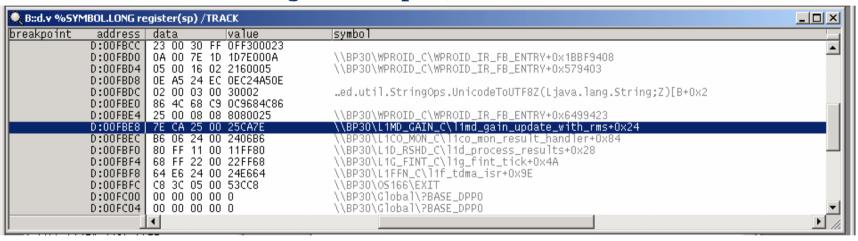

#### Lauterbach: how to use the function call stack

To show it, the .cmm file shall include at the end:

d.v %SYMBOL.LONG register(sp) /TRACK

■ Sometimes, expecially when traps occur or when the system stops in the Apoxi area, a 2 byte offset has to be applied to the SP in order to see the correct stack:

d.v %SYMBOL.LONG register(sp)+2 /TRACK

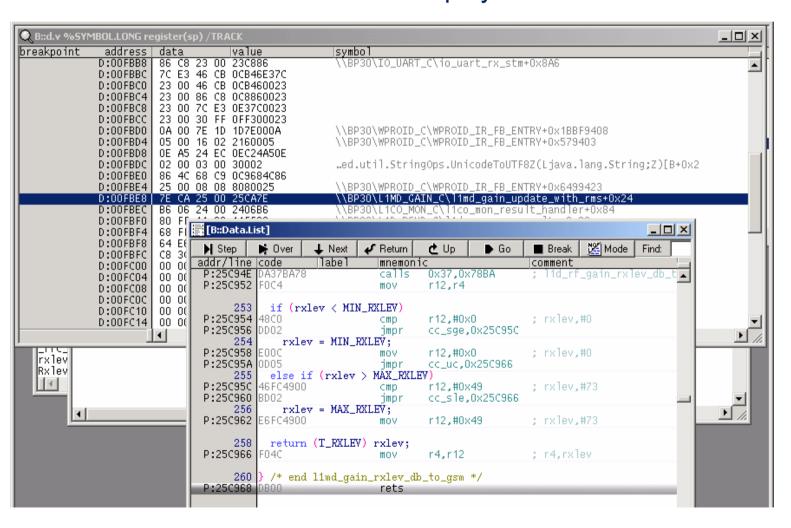

## Lauterbach: how to use the function call stack (2)

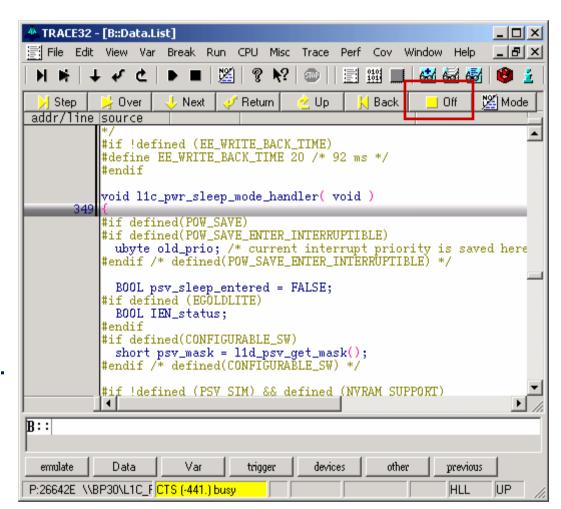

The current instruction can be displayed with View/List Source

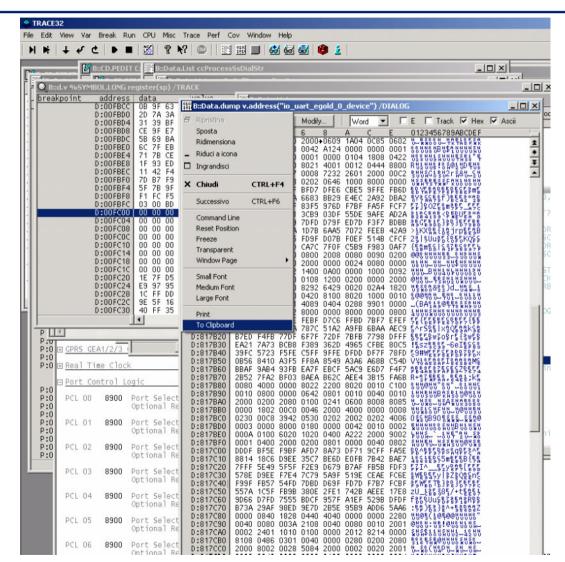

#### Lauterbach: how to save a data dump

To save any information on a text file, you can dump the symbol:

# Lauterbach: how to save a data dump (2)

- You can save it to clipboard by clicking on the upper left corner of the dump window with the left button of the mouse.

- Then you can paste it to a file

- If you have compiled with DEBUG option, you can copy the view/watch window where the variable is displayed by using the same procedure.

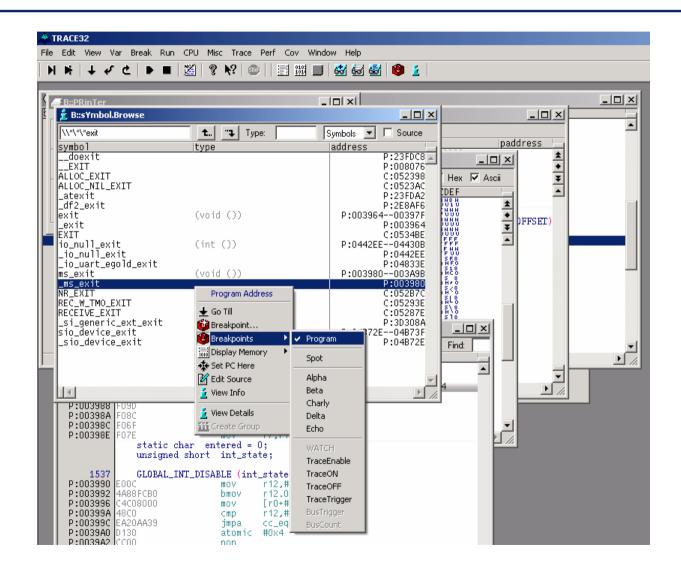

#### Power Trace: how to save a backtrace

Set a program BP e.g. at symbol \_ms\_exit

## Power Trace: how to save a backtrace (2)

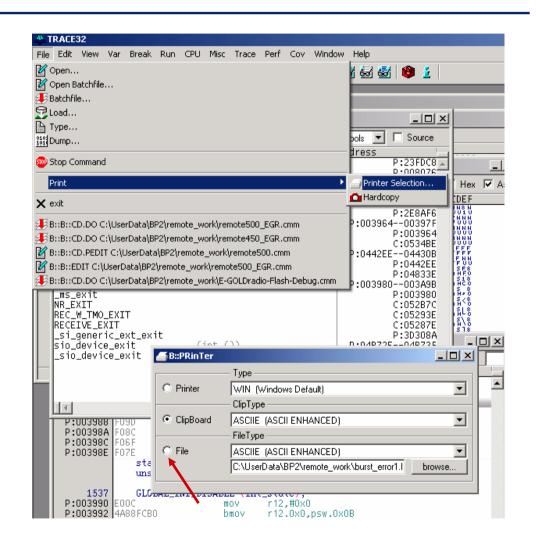

- When the system stops, select the item "File→Print→Printer selection".

- Select a name with a numeric suffix, so that its number is automatically updated every time you print.

### Power Trace: how to save a backtrace (3)

- Then type the following command winprint.Trace.List (-<index>.)--(-0) DEFAULT ti.ref

- Pay attention to the "minus" (the index is negative) and to the "dot" at the end if you use the decimal format.

#### Power Trace: how to use a backtrace

- You can simulate the recorded execution in a stepby-step fashion. The contents of the variables and the registers are updated but not fully reliable.

- Simply select the point where you would like to start, press right-click and SET CTS

```

TRACE32 - [B::Trace.List ALL]

Edit View Var Break Run CPU Misc Trace

Perf Cov Window Help

010:

101:

$ 5 5

Find...

🔑 Setup...

∩ Goto...

## Chart

More

record

T_PSV_STATE psv_state;

psv_state = l1d_psv_tick();

615

** RETURN VALUE:

#if !defined (EE_WRITE_BACK_TIME)

#define EE WRITE BACK TIME 20 /* 92 ms */

void l1c_pwr_sleep_mode_handler( void )

Analyzer

.R. ▶ Set Ref

** Do no

s globally at this point.

** Inste, 3 Set Zero

priority. This way, high

ÚMTS AFC can still be handled.

prior

Set CTS

prio(INT_PRIO_VERYHIGH);

old_prio 📿 View

CER_INTERRUPTIBLE) */

if (IEN_: no Timing

tendif

L1_DIS

Ignore in Statistic

#endif /* |

NTER INTERRUPTIBLE) */

Use in Statistic

l1c_pwr_: here

wr_calc_sleep_time();

** PARAMETERS:

** RETURN VALUE:

maximum system sleep time

#if defined (POW_SAVE)

static ushort l1c_pwr_calc_sleep_time( void )

218

&& psv_control_state == PSV_NORMAL_MODE

#if defined(GSM) || defined(GPRS)

```

## Power Trace: how to use a backtrace (2)

- To start the step-bystep execution, use View/List Source.

- Pay attention that, if you select the HLL source only mode, you can miss passages to non-symbolic functions. Besides, the interruptions by LISRs are not handled.

- Press Off to exit CTS mode and possibly change the starting point.

### Tips on the Power Trace: effects of the page mode

- Unfortunately the trace.list output of the Power Trace is fully correct only when the page mode is disabled.

- If the page mode is active, as it happens in our released SW, occasionally (at most 3 out of 4) consecutive *opcode fetch* instructions can be lost.

- Therefore, to get a complete and reliable backtrace enter (via Mobile Analyser of AT command window) the command:

AT+XL1SET="PAGEMODE OFF"

- To be able to explore rapidly and effectively the backtrace to look for unexpected behaviors, you can open it with Source Insight and look for the references of the string "calls".

- This holds of course if the page mode is disabled. Otherwise a few call instructions could be missing.

- Pay attention in general that ASM instructions can be only fetched due to proximity and not actually executed.

### Parsing a backtrace

```

+ calls

0x9,0xC1D4

; mac handle rlc data block

0x0,0xA842 ; PS cccl 0362 04

calls

calls

0x15,0x2F7C ; retrieve timer

+ calls

0x5,0x242A

; wait sem

calls

0x5,0x3274

; WAIT SEM

+ calls 0x9,0xC170

; mac handle persistence level change

0x0,0x87A4 ; PS cccl 0065 03

calls

+ calls

0x0B, 0xF850; mac tm get tbf mode

calls

0x0,0xC3D2; ms exit

switch( mac tm get tbf mode() )

case AT EGPRS:...

break;

case AT GPRS:

retrieval basket.mSlotCl = data base.ms multislot class gprs;

break;

default: ...

if( retrieval basket.mSlotCl == NO MULTI SLOT CAPABILITY) /*zero*/

ms except (MS UNKNOWN ERROR);

```

# Parsing a backtrace (2)

- Since the element data\_base.ms\_multislot\_class\_gprs has a fixed value for the whole system life, an unwanted memory overwriting should have occurred (casually to 0).

- We look for operations on the element, whose offset is 0x20:

```

D:837AAA opfetch 00 \\BP30\MAC_IM_C\_data_base+0x20

```

■ If we are lucky and the overwriting happened within the sampled interval of ca 2 seconds, we will find ("may" if we have not disabled the page mode) for instance:

- In this case the cause was an overrun of the user stack of the I1f\_tdma\_isr process which interrupted the MAC processing;

- The fix was to increase its user stack in file os166.con to 1500:

```

%PRI_PROC l1f_tdma_isr,

C, 1500, 128, 1

```

#### Note on Write BP

- Write BP can be useful to debug the above-mentioned type of errors, although the overwriting can affect different memory areas.

- If you want to break at writing of a specific value, you can rely on conditioned BP, but this implies <u>high delays</u> for the Lautebach to verify the condition:

- You have to work with sev=0,

otherwise the system crashes

- Same problem with counters

- Shortcut: set a BP specifying the data → no delay

# Parsing a backtrace: timings of function calls

You can collect information on the timings of the functions.

```

calls 0xDB,7396 ; ms_error

calls 0x24,0x5B04; fcb completed \rightarrow next slide

ls 0x24,0x6184 ; lld_lfcb_stm_check_decoder 0x26,0x20D8 ; llx_lisr2_actions

D:801225 \\BP30\Global\ l1f tdma isr -3.345ms

D:051C12 \\BP30\OS166\OS166 \VCR 43+0x40 -3.601ms

0x7,0xD99C ; llx lisr1 actions

calls

calls 0x38,0x13DA ; cmd int 2 dsp

0x26,0x20D8 ; l1x lisr2 actions

calls

calls 0x38,0x1B68 ; l1d_add_msg_2_buf

calls

0x26,0x4C2C ; 11d dsp fcb init

D:801225 \\BP30\Global\_l1f_tdma_isr_ -8.012ms

D:051C12 \\BP30\OS166\OS166 \VCR 43+0x40 -8.216ms

calls 0x7,0xD99C ; llx lisr1 actions

```

# Parsing a backtrace: timings of function calls (2)